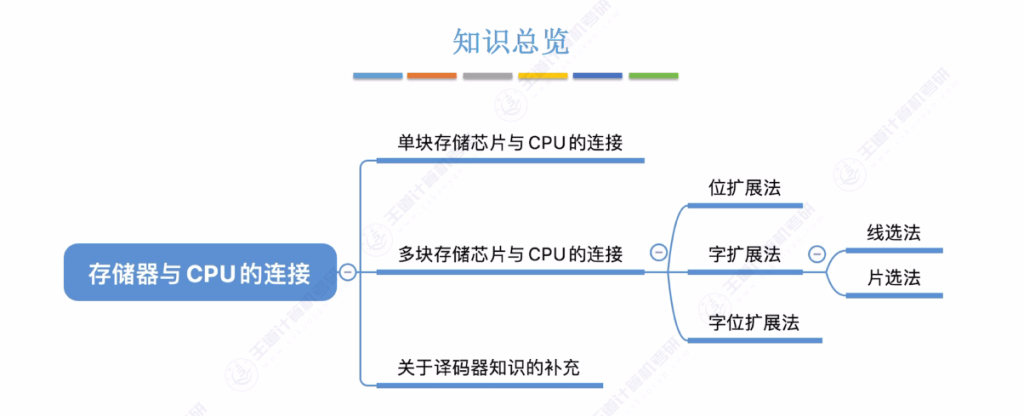

一、主存储器与CPU的连接

1.1 知识总览

- 核心内容:本节主要学习主存储器与CPU的连接方法,包括单块存储芯片连接、多块存储芯片连接(位扩展、字扩展、字位扩展)以及译码器补充知识

- 学习建议:内容较硬核,建议结合课本反复学习并配合课后习题巩固

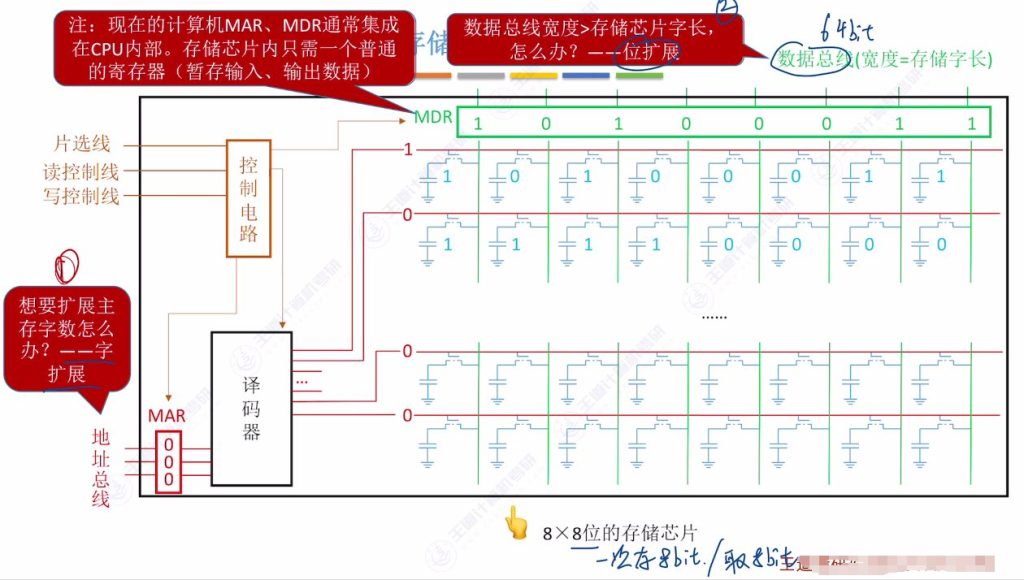

1.2 单块存储芯片与CPU的连接

- 数据接口:通过绿色数据总线与CPU连接,宽度等于存储字长(示例中为8位)

- 地址接口:通过红色地址总线连接,示例为8×8位芯片(8个字,每字8位)

- 控制信号:包含片选线、读写控制线,通过控制总线传输

- 寄存器位置:现代计算机中MAR和MDR通常集成在CPU内部

1.3 字扩展法解决字数扩展问题

- 应用场景:当需要扩展主存字数(存储单元数量)时使用

- 实现原理:通过连接多块存储芯片增加总存储单元数量

- 示例说明:8×8位芯片只能存储8字节,通过字扩展可增加存储容量

1.4 位扩展法解决字长扩展问题

- 应用场景:当存储芯片字长小于数据总线宽度时(如现代64位CPU)

- 实现原理:多块芯片并行连接,使总存储字长匹配数据总线宽度

- 性能优化:保持数据总线宽度与存储字长一致可提高读写速度

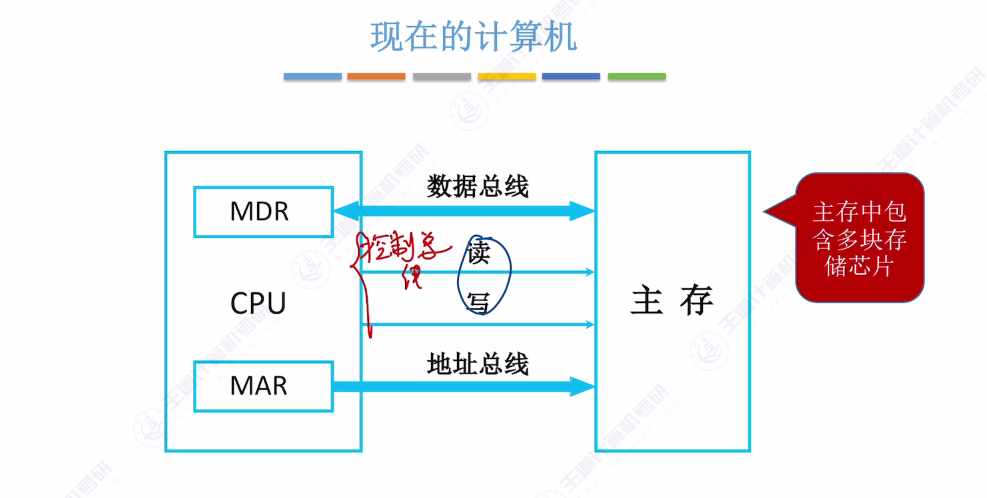

二、现代计算机中MDR与MAR的位置

- 寄存器位置:MDR存储读写数据通过数据总线交换,MAR存储地址通过地址总线传输

- 控制信号:CPU通过控制总线发送读写控制信号

三、多块存储芯片与CPU的连接

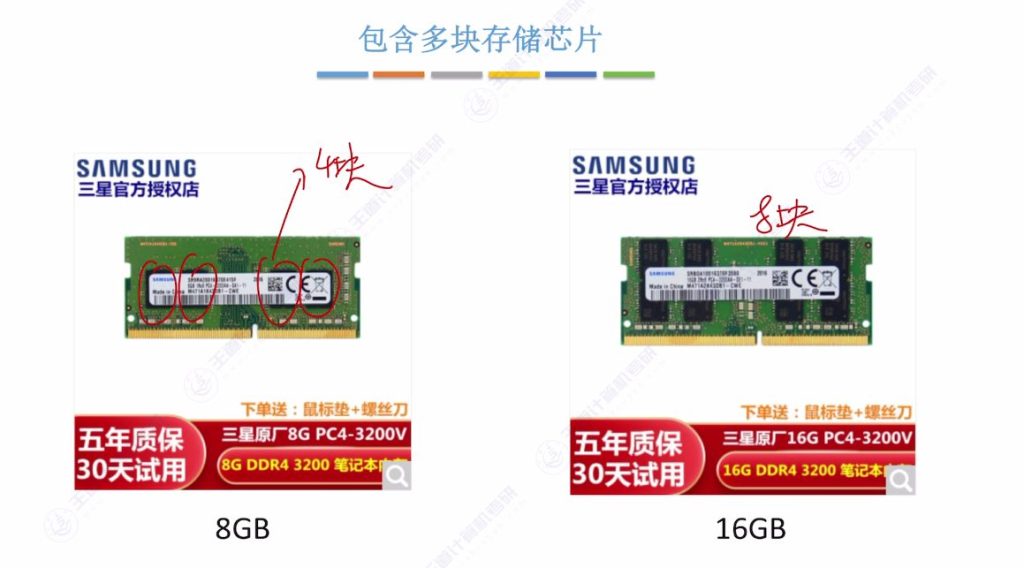

- 实际应用:商业内存条(如8GB含4芯片,16GB含8芯片)采用多芯片连接

- 现实意义:多芯片连接方案直接影响内存性能和容量扩展

四、存储芯片信号命名与解释

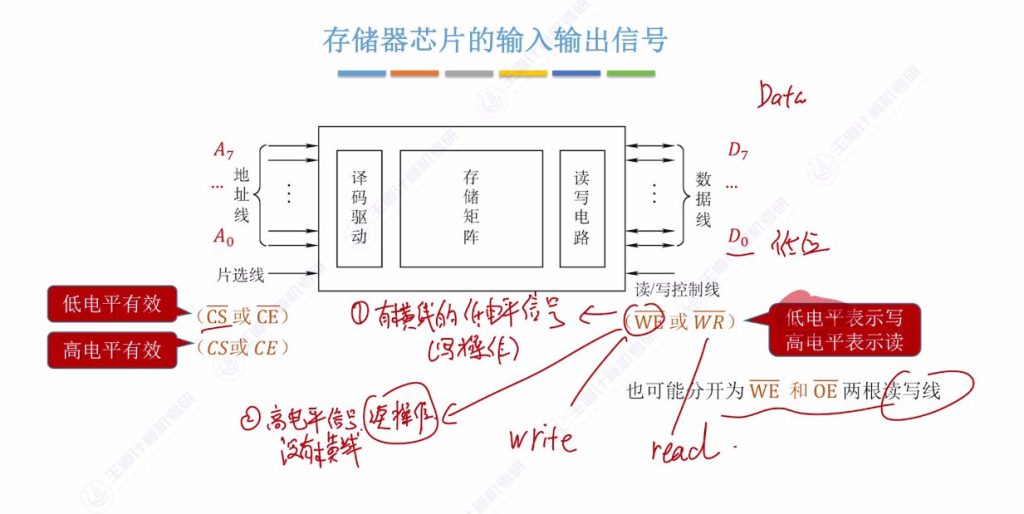

- 地址信号:用A表示(A0-A7等),A0为最低位

- 数据信号:用D表示(D0-D7等),D0为最低位

- 片选信号:常用CS(或CE)表示,横线表示低电平有效

- 读写信号:WE/WR(写使能) – write enable\write read,OE(读使能),低电平有效

- 信号约定:需注意信号表示方式(有无横线)对应的电平有效性

五、增加主存的存储字长-位扩展

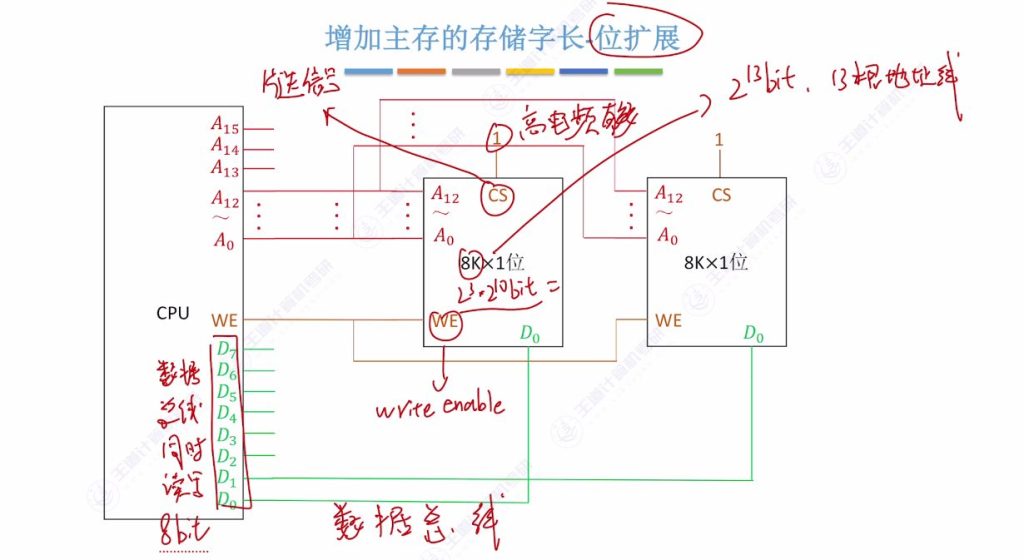

5.1 地址线的连接

- 地址计算:8K存储单元需要13位地址线(213=23*210)

- 连接方式:CPU地址总线A0-A12直接连接所有芯片的对应地址引脚

5.2 读写控制信号的连接

- 信号解释:WE无横线表示高电平写有效,低电平读有效

- 连接方式:CPU读写控制信号通过控制总线并行连接所有芯片

5.3 片选信号的连接

- 单芯片情况:直接接高电平(CS高电平有效)

- 结果:存储字长1位,数据总线利用率低

六、增加主存的存储字长 – 位扩展

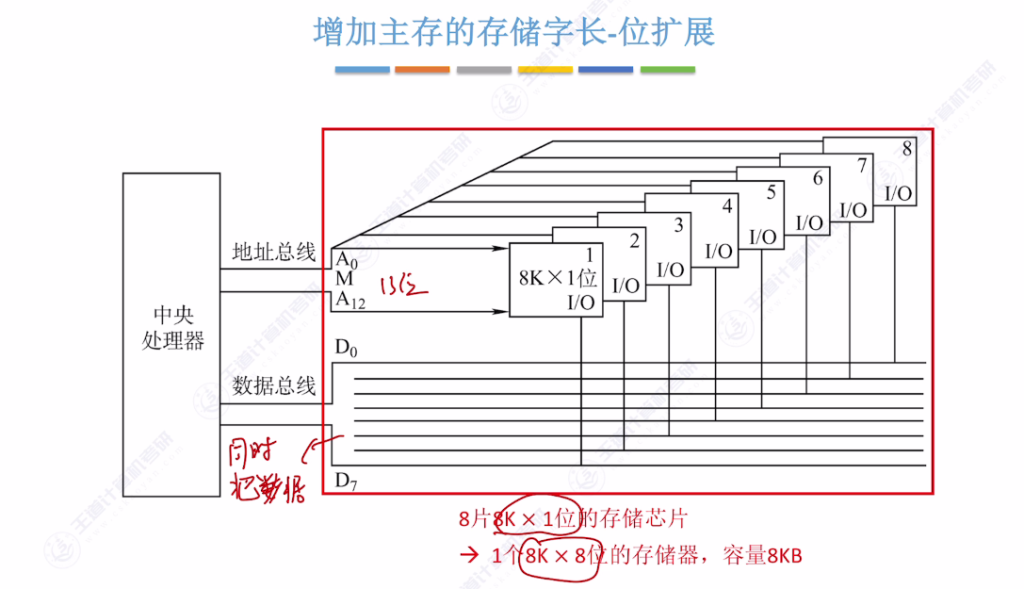

- 扩展方法:添加相同型号芯片(8K×1位)

- 连接特点:

- 相同地址线连接所有芯片

- 读写信号并联

- 片选信号并联接高电平

- 扩展效果:存储字长扩展为2位,可同时读写2位数据

位扩展的具体实现方式

- 最终方案:使用8片8K×1位芯片组成8K×8位存储器

- 连接细节:

- 所有芯片地址线A0-A12并联

- 读写控制线WE并联

- 各芯片数据线分别连接数据总线不同位

- 总容量:8KB(8K×8位)

- 术语定义:这种连接方式称为”位扩展”

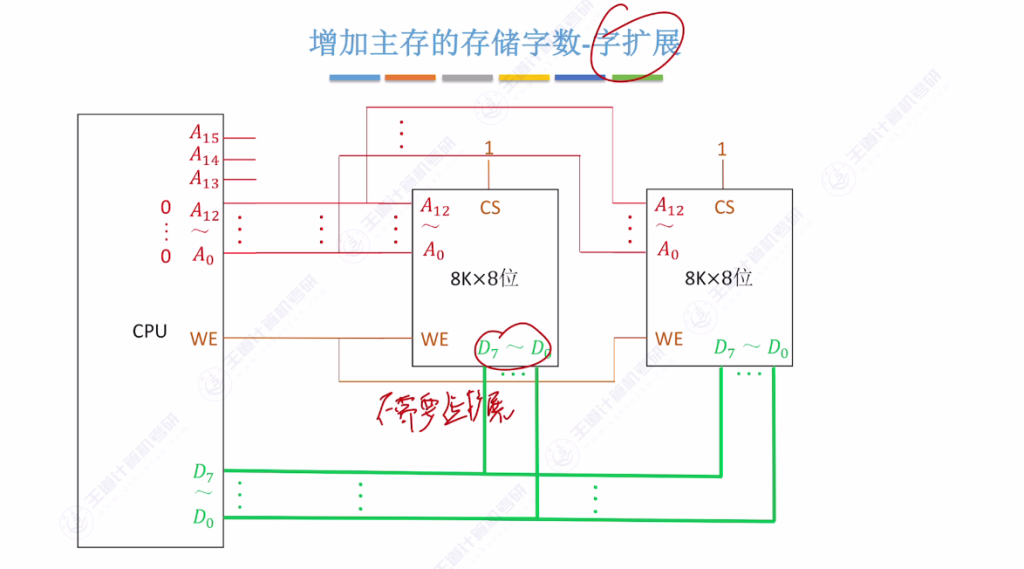

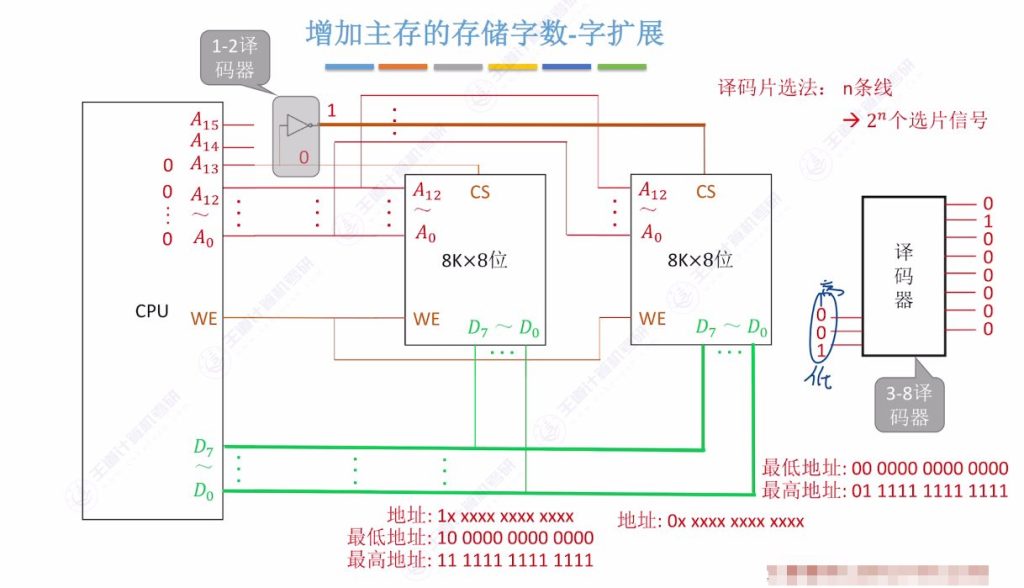

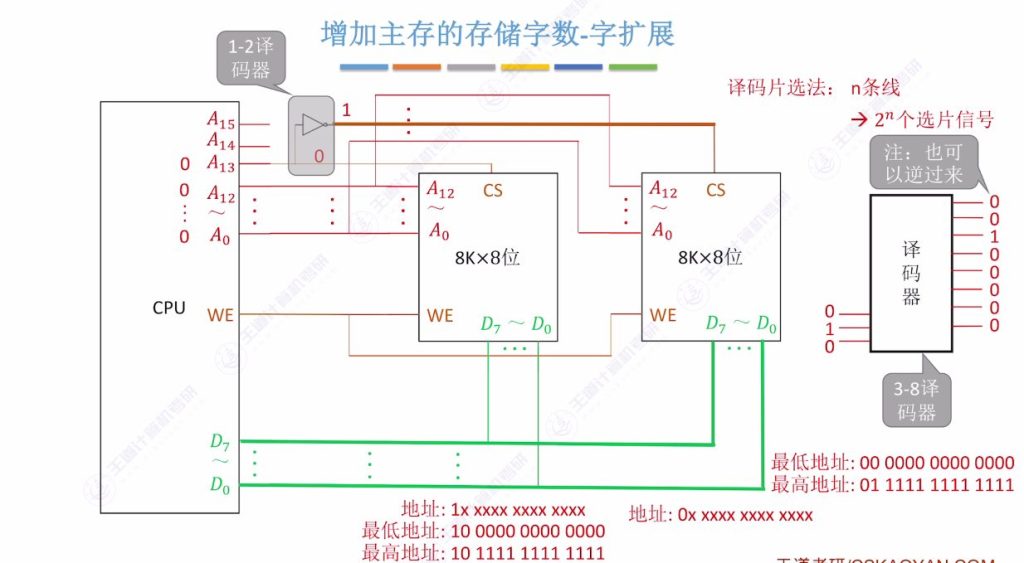

七、增加主存的存储字数-字扩展

7.1 存储芯片与CPU的匹配

- 字长匹配:当使用 8K×8 位存储芯片时,其8位数据宽度与CPU的8位数据处理能力完美匹配,无需进行位扩展。

- 地址线需求:8K存储单元需要13位地址线(213),剩余高3位地址线未利用。

7.2 CPU寻址能力的利用

- 寻址能力浪费:16位地址总线的CPU(216寻址能力)仅使用13位,剩余3位未利用。

- 扩展思路:通过添加同型号芯片,利用高位地址线实现存储单元数量的扩展。

7.3 字扩展的方法

- 基础连接:将新增芯片的低13位地址线与原芯片并联,数据总线并联,读写控制信号共享。

- 冲突问题:直接并联会导致多芯片同时响应相同地址,造成数据总线冲突。

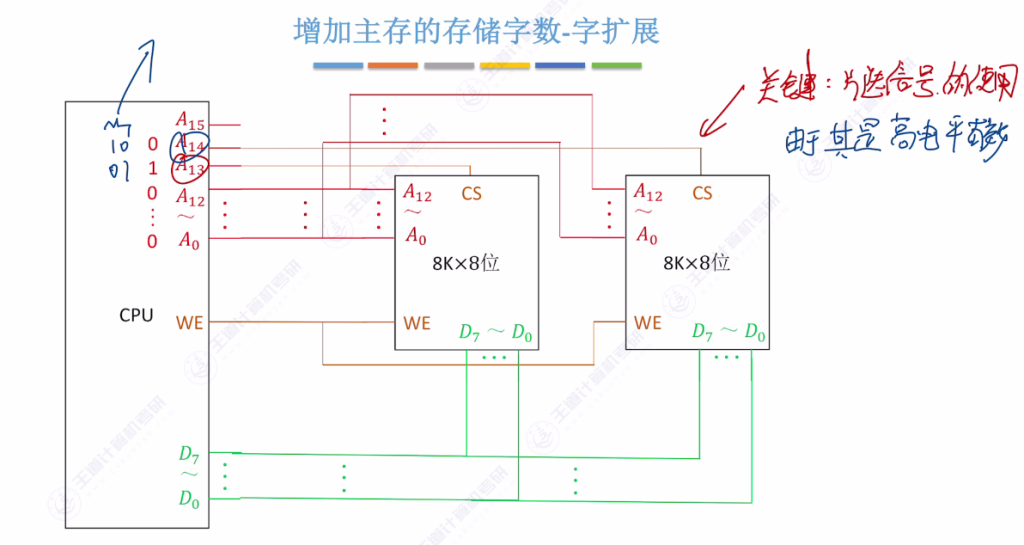

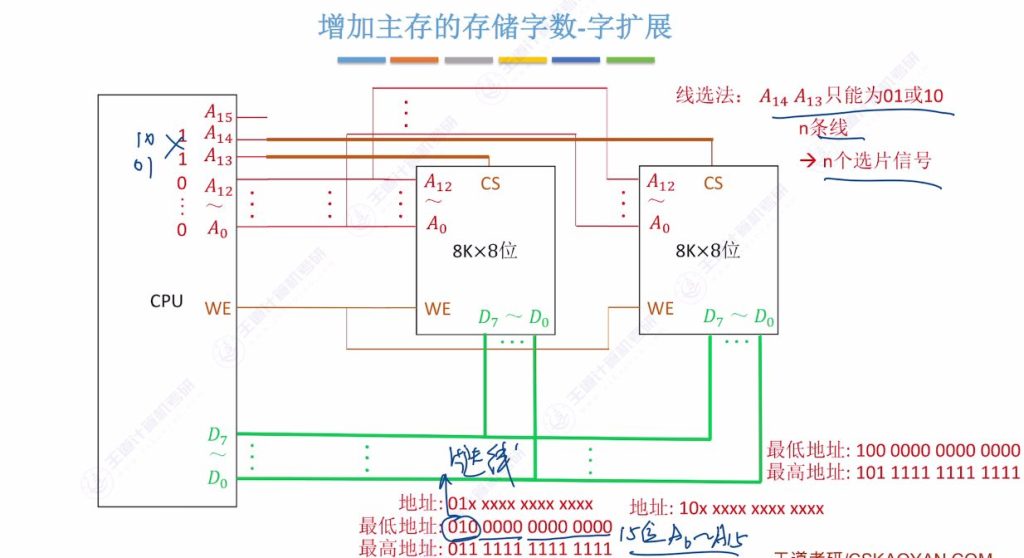

7.4 线选法及其问题

- 实现方式:用高位地址线(如A13、A14)直接作为片选信号:

- 有效组合:仅允许01(选中左芯片)或10(选中右芯片)

- 无效组合:00和11会导致地址空间不连续(00和11开头的地址不可用)

- 局限性:n条多余地址线只能产生n个片选信号,地址空间碎片化。

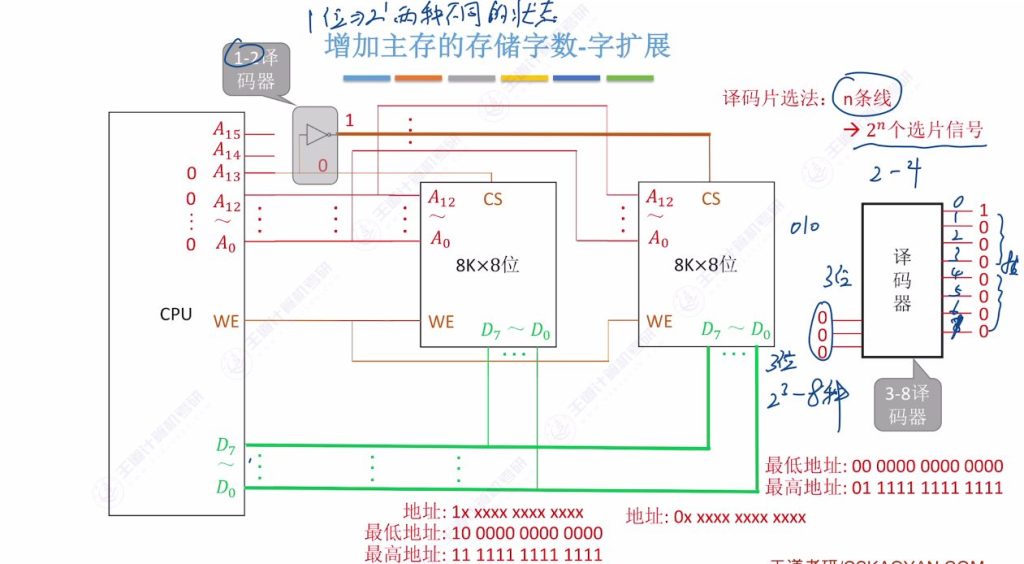

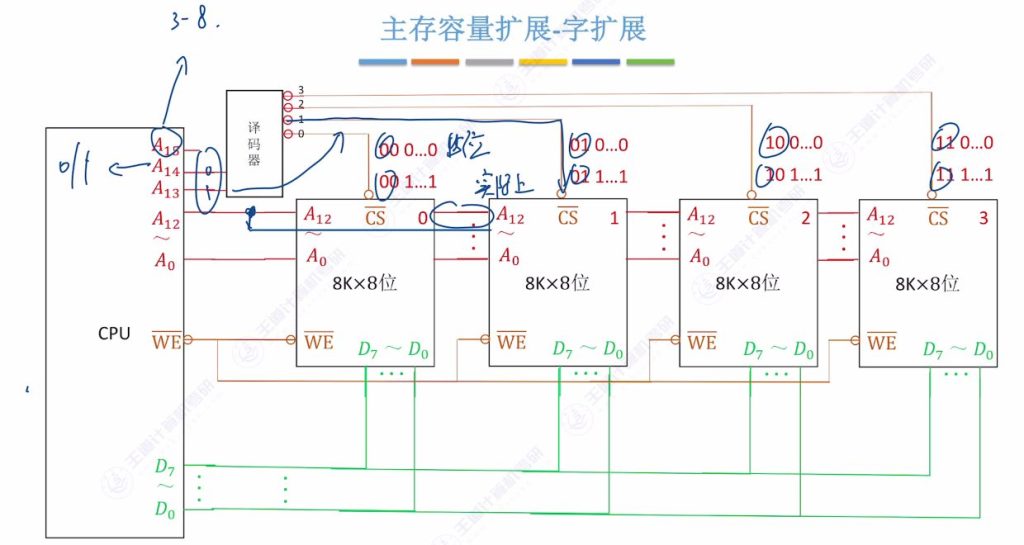

7.5 译码器片选法

- 电路改进:在A13线路增加非门,构成1-2译码器:

- A13=1时:左芯片工作(地址范围1xxxxxxxxxxxxx)

- A13=0时:右芯片工作(地址范围0xxxxxxxxxxxxx)

- 优势:实现地址空间连续(全0到全1)

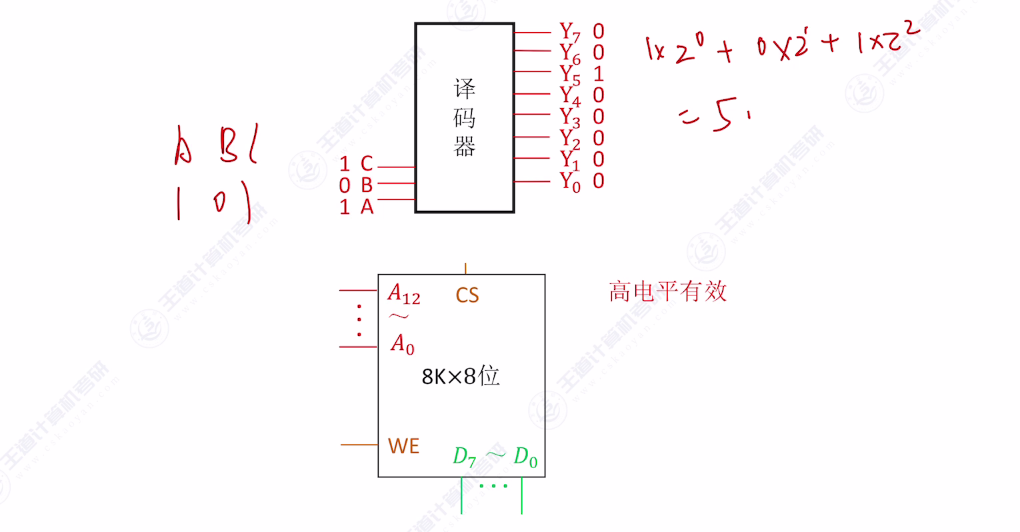

7.6 译码器的工作原理

- 命名规则:

- 1-2译码器:1位输入→2种输出状态

- 3-8译码器:3位输入→8种输出状态(如A13-A15)

- 输出特性:任何时候只有一条输出线有效(低电平),其余为高电平

- 信号表示:CS上加横线/小圆圈表示低电平有效

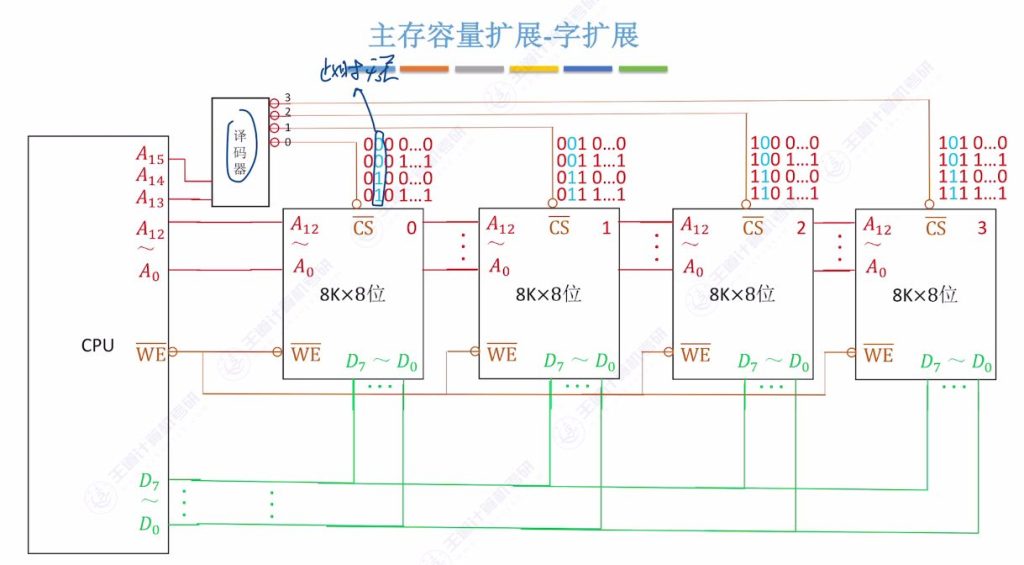

7.7 二四译码器的应用

- 地址分配:

- 00→第一片(地址范围000xxxxxxxxxxxxx)

- 01→第二片(地址范围010xxxxxxxxxxxxx)

- 10→第三片(地址范围100xxxxxxxxxxxxx)

- 11→第四片(地址范围110xxxxxxxxxxxxx)

- 异常接法:若以A13+A15作为译码输入,会导致:

- 每片芯片对应16K地址空间(实际只有8K)

- 地址重叠(A14取值不影响片选)

7.8 主存容量扩展-字扩展

- 线选法:

- 优点:电路简单(n线→n个片选)

- 缺点:地址空间不连续,利用率低

- 译码片选法:

- 优点:地址空间连续(n线→2n个片选)

- 缺点:需要额外译码电路

未扩展与字扩展的总结

- 位扩展:增加数据字长,提升总线利用率

- 字扩展:增加存储单元数量,充分利用CPU寻址能力

- 组合应用:两种方法可结合使用实现主存容量的多维扩展

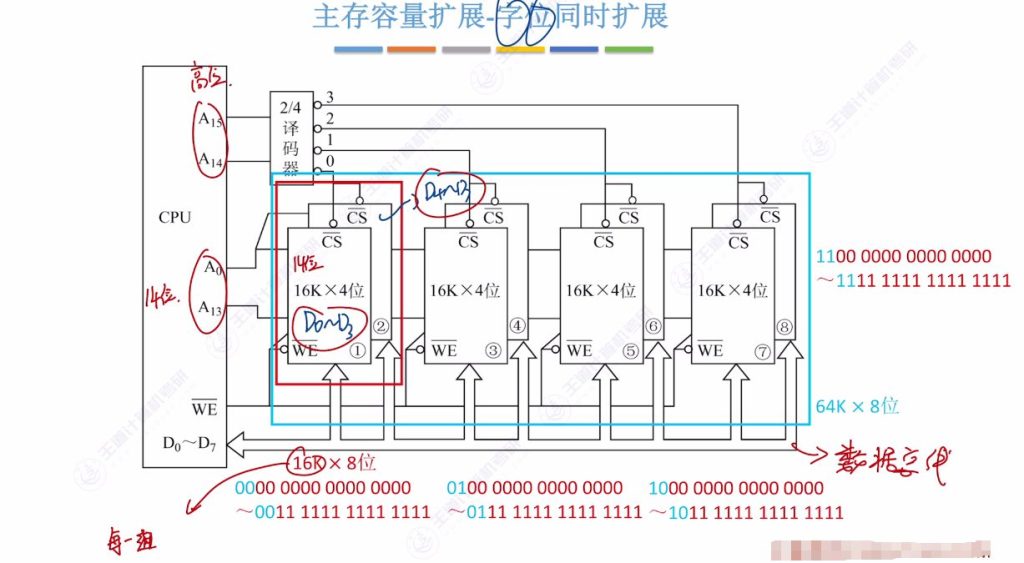

八、增加主存的存储字数和字长-字位同时扩展

- 基本原理:通过组合字扩展和位扩展技术,同时增加存储器的字数容量和字长位数

- 芯片组配置:

- 使用8块16K×4位存储芯片

- 每2块芯片组成一组实现位扩展(共4组)

- 每组通过2-4译码器实现字扩展

- 位扩展实现:

- 每组中第一块芯片连接数据线D0∼D3

- 第二块芯片连接数据线D4∼D7

- 组合后每组提供8位数据宽度

- 字扩展实现:

- 芯片内地址使用CPU的A0∼A13(214=16K)

- 高位地址A14、A15接入2-4译码器

- 译码器输出4个片选信号控制4组芯片

- 地址空间分配:

- 第一组:00开头(地址范围0000H∼3FFFH)

- 第二组:01开头(地址范围4000H∼7FFFH)

- 第三组:10开头(地址范围8000H∼BFFFH)

- 第四组:11开头(地址范围C000H∼FFFFH)

- 系统特性:

- 总容量:64K×8位(4组×16K×8位)

- 地址空间连续不间断

- 字长完美匹配CPU的8位读写能力

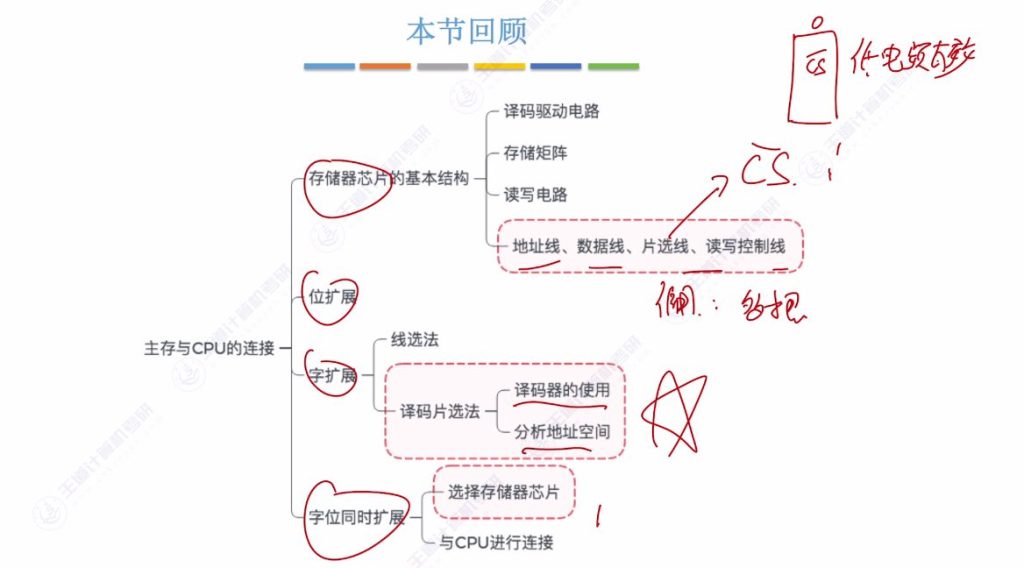

九、内容回顾

- 存储芯片基本结构:

- 核心组件:存储矩阵、译码驱动电路、读写电路

- 外部接口:地址线、数据线、片选线(CS)、读写控制线(WE)

- 注意:片选信号需明确有效电平(低电平有效需标注小圆圈)

- 扩展方法比较:

- 位扩展:增加数据位宽,地址线不变

- 字扩展:增加存储单元数量,使用译码器产生片选

- 字位同时扩展:组合上述两种方法

- 重点考察内容:

- 译码器使用:根据输入输出分析芯片地址空间

- 地址空间计算:需掌握2n的容量换算

- 芯片选择:字位扩展中的芯片组合方式

- 连接方法:线选法 vs 译码片选法

- 实践应用:

- 课后习题将重点考察:

- 译码器连接分析

- 地址空间划分

- 字位同时扩展的芯片配置

- 课后习题将重点考察:

十、补充译码器知识

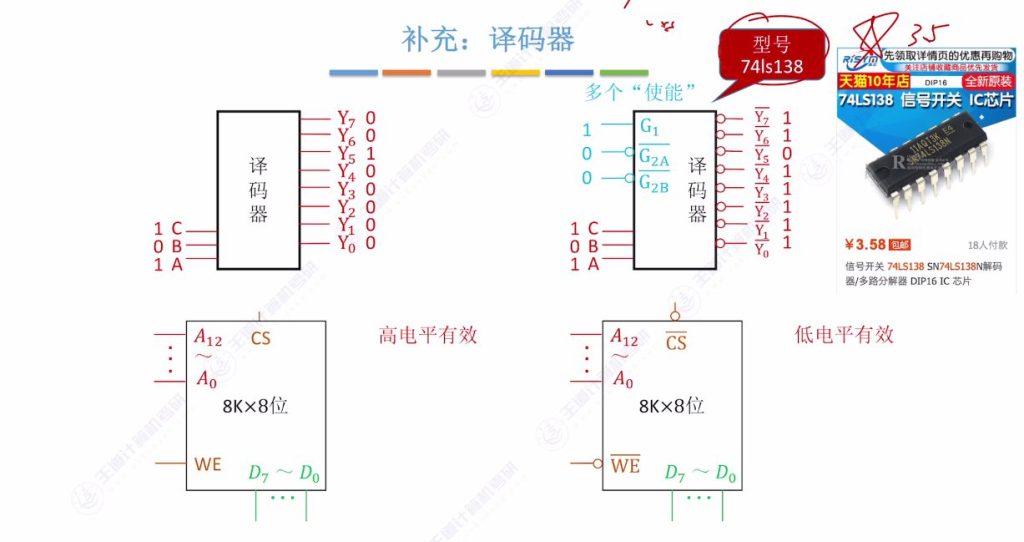

10.1 三八译码器的基本功能

- 输入输出结构:具有3个输入端和8个输出端,输入信号A2A1A0可表示8种状态

- 工作特性:给定输入信号后,仅对应的一条输出线为高电平(有效信号),其余保持低电平

- 应用场景:适合与高电平有效的存储芯片配合使用,因其有效输出信号为高电平

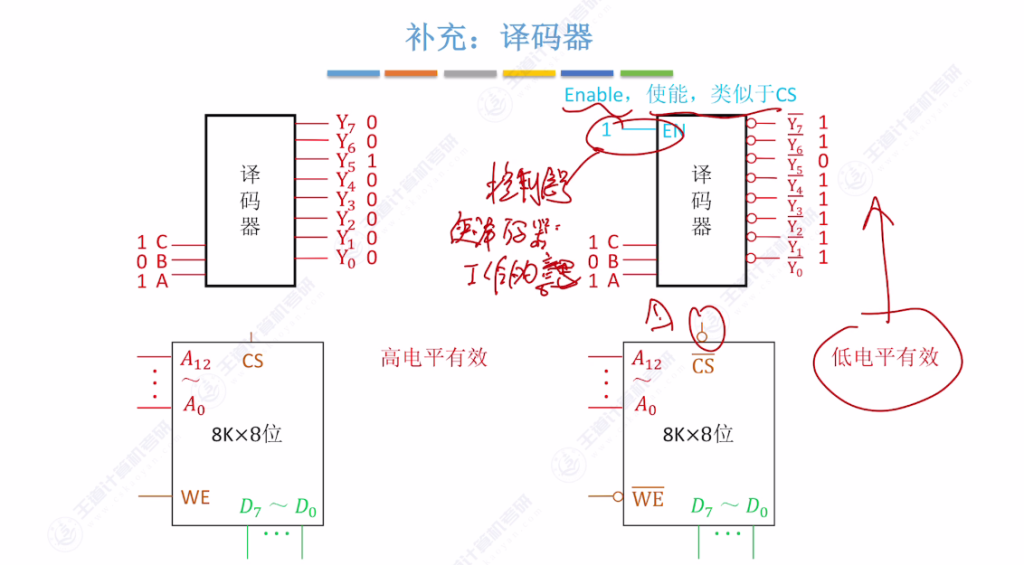

10.2 译码器的两种画法与电平有效性

- 输出极性标识:

- 无圆圈:输出有效信号为高电平(默认情况)

- 带圆圈:表示输出信号取反,有效信号为低电平

- 匹配原则:

- 高电平有效译码器需搭配高电平有效芯片

- 低电平有效译码器需搭配低电平有效芯片

- 关键注意:设计时必须明确电平有效性,否则会导致逻辑错误

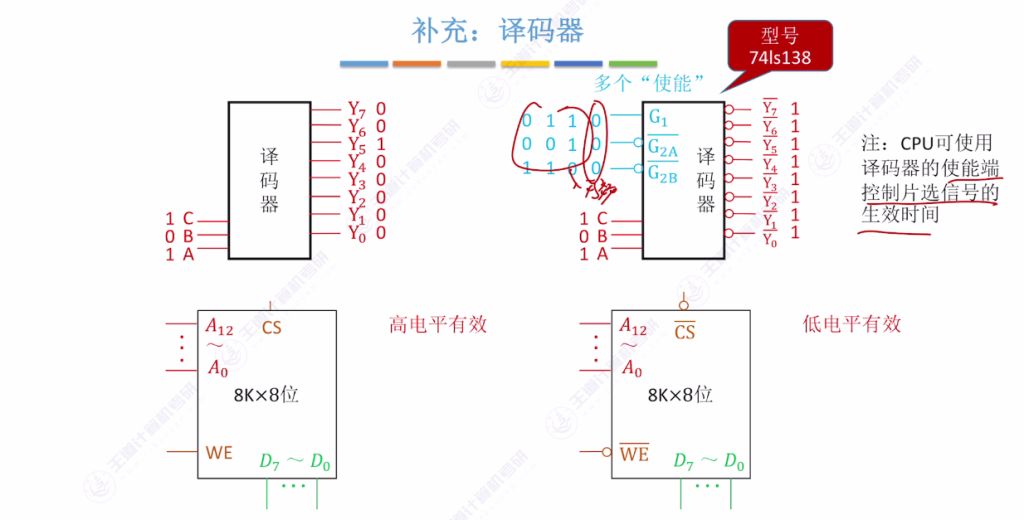

10.3 译码器的使能端

- 基本功能:

- 使能端(EN)控制译码器工作状态

- 无圆圈表示高电平有效(与片选信号类似)

- 多使能端设计:

- 可能包含多个使能端(如74LS138有3个)

- 各使能端可能有不同有效电平(需同时满足条件)

- 工作条件:

- 当所有使能条件满足时译码器才工作

- 任一使能条件不满足则所有输出保持无效状态

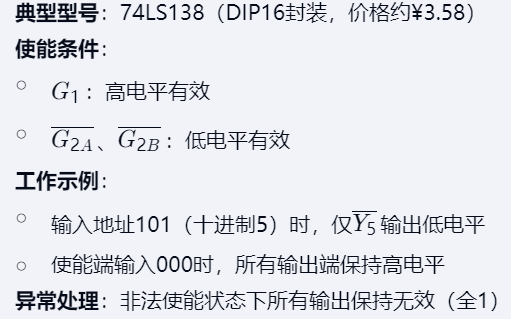

10.4 74LS138译码器实例

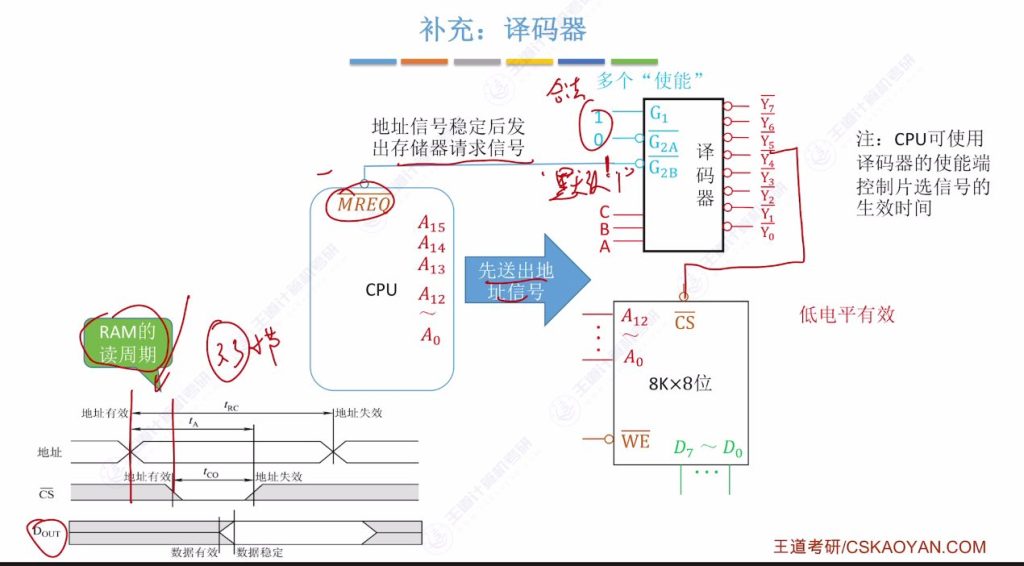

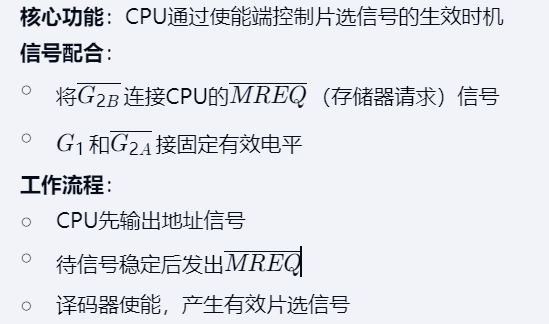

10.5 译码器使能端控制片选信号的应用

CPU与主存的配合工作原理

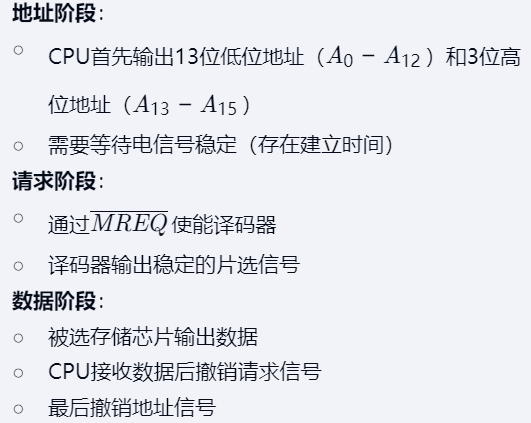

RAM读写周期与时序图的理解

- 时序要素:

- 地址有效:信号稳定前存在波动(图中上下摆动)

- 片选信号:高电平无效(黑色),低电平有效(白色)

- 数据输出:有效期为白色区域,数据含0/1变化

- 关键时间点:

- t0:地址信号开始输出

- t1:地址稳定后发出片选

- t2:数据开始输出

- t3:CPU撤销请求

- t4:最终撤销地址

- 设计意义:确保存储芯片接收稳定地址后才被选通

本网站原创文章版权归何大锤的狂飙日记所有。发布者:何大锤,转转请注明出处:何大锤的博客