一、总线的基本概念

1.1 为什么要用总线

原因:分散连接问题

- 连接复杂度:数量庞大

- 物理限制:大量接口占用空间,印刷电路板实现困难

- 扩展性差:新增设备需与所有原有模块连接,增加 n 组线路

1.2 什么是总线(Bus)

总线是连接各个部件的信息传输线,是各个部件共享的传输介质

- 基本定义:

- 物理本质:一组信息的公共传输线(英文Bus即公共汽车)

- 工作特性:任何时刻只能有一对设备使用总线,存在总线争用问题

总线优势

- 简化连接:所有设备共享一组公共传输线

- 降低成本:减少线路数量和接口空间占用

- 便于扩展:新设备只需接入总线即可与系统通信

1.3 总线信息的传输

两种方式:串行传输、并行传输

串行传输:逐位传输,适合长距离(机器间通信),抗干扰强

并行传输:多位同时传输,适合短距离(机箱内部),需多条数据线

现代趋势:高速信号传输多采用串行方式

拓展:

性能对比:

并行传输局限:长距离时信号线间干扰导致波形畸变

串行优势:通过提高单通道速率弥补位数劣势

技术发展:

并行改进:需特殊技术措施延长有效传输距离

应用选择:根据距离、速率需求选择合适传输方式

二、总线结构的计算机举例

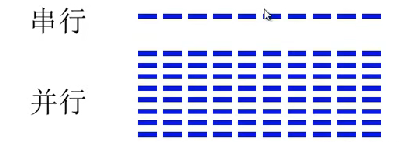

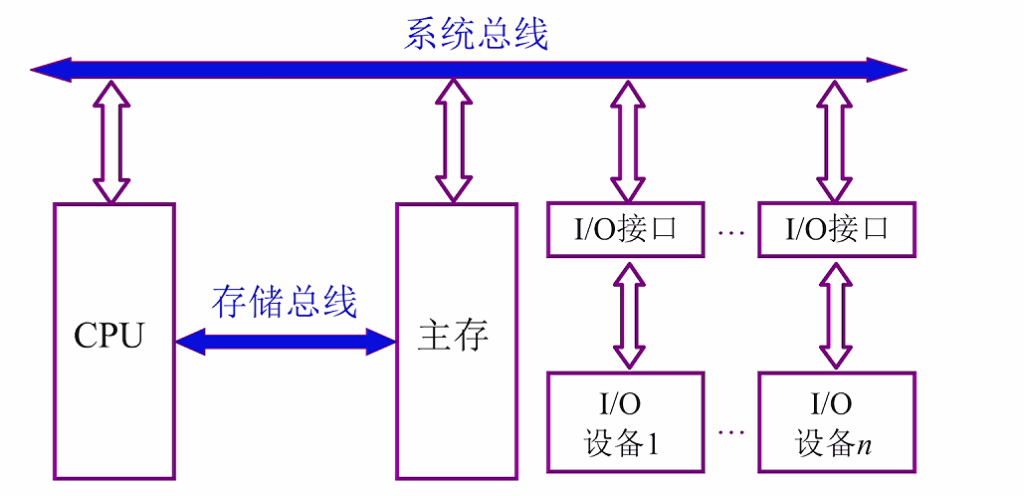

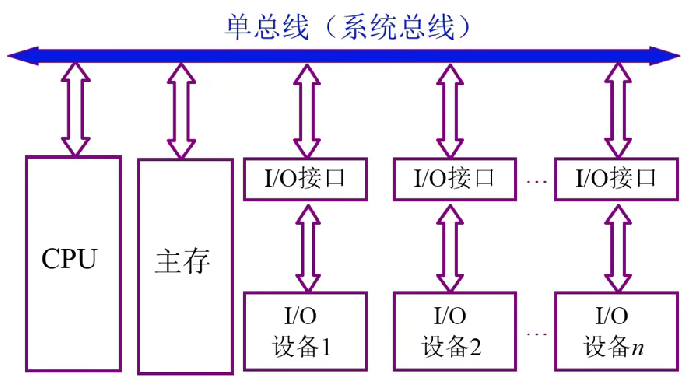

2.1 单总线结构框图

- 结构特点:

- 统一连接:CPU、主存、I/O设备全部挂接单一系统总线

- 简单经济:结构简单,实现成本低

- 性能瓶颈:

- 带宽限制:所有数据传输共享同一总线带宽

- 延迟问题:远距离设备通信延迟显著

- 冲突严重:主存与I/O传输时CPU需等待

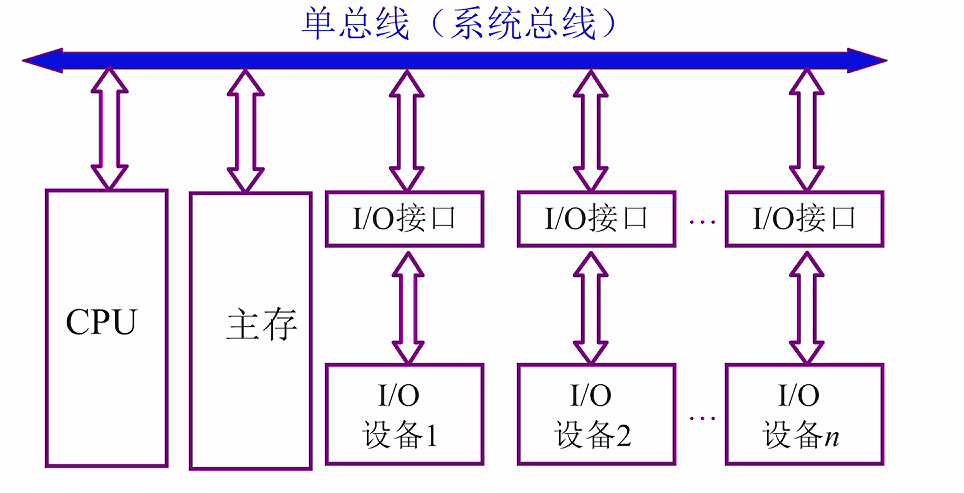

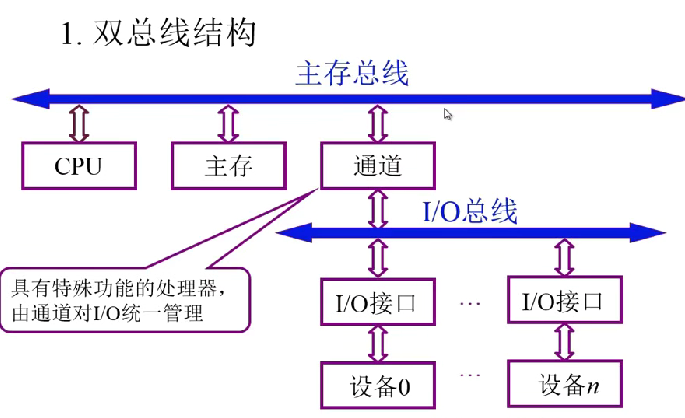

2.2 面向CPU的双总线结构框图

- 结构改进:

- 专用通道:CPU与主存间增设存储总线(M总线)

- 分离设计:I/O设备通过独立I/O总线连接

- 现存问题:

- 间接传输:主存与I/O设备通信仍需CPU中转

- 效率影响:DMA操作仍会打断CPU执行

2.3 以存储器为中心的双总线结构框图

- 优化设计:

- 双通道架构:系统总线与存储总线并行

- 直接通路:主存可直接与I/O设备通信

- 技术限制:

- 分时工作:传统存储器无法同时响应两条总线

- 未来展望:双端口RAM技术发展可能突破此限制

三、总线的分类

3.1 根据总线的位置分类

1)片内总线 – 芯片内部的总线

- 定义范围:在芯片内部连接不同功能部件的总线

- 功能特点:专门用于集成电路内部各模块间的数据传输

2)系统总线 – 计算机各部件之间的信息传输线

3)通信总线(外部)- 用于计算机系统之间或计算机系统与其他系统之间的通信

- 连接范围:计算机之间或计算机与其他设备间的连接总线

- 系统扩展:用于构建更大规模的系统

- 传输方式:

- 串行数据通信

- 并行传输

- 应用场景:跨系统、跨设备的远距离数据传输

3.2 系统总线根据信号传输的不同(计算机内部)

1)数据总线 – 双向、与机器字长、存储字长有关

- 传输内容:专门传输数据信号的总线

- 方向特性:通常为双向传输(CPU←→外设/存储器)

- 宽度关系:总线宽度≤机器字长/存储字长(如64位机可用8位总线)

- 传输机制:窄总线需多次传输完成大数据量操作(如8位总线传64位数据需8次)

2)地址总线 – 单向、与存储地址、I/O地址有关

- 功能特性:用于寻址存储单元或I/O设备

- 方向特性:通常为单向(CPU→外设/存储器)

- 宽度决定:地址线数量与存储地址空间直接相关

- 典型实现:在模型机中与MAR寄存器宽度保持一致

3)控制总线 – 有出、有入

- 信号类型:包含控制信号和状态信号

- 方向特性:双向传输(既有CPU输出也有外设输入)

- 典型信号:

- 输出信号:存储器读写控制、总线许可、中断确认

- 输入信号:中断请求、总线请求等外设状态信号

四、总线的特性及性能指标

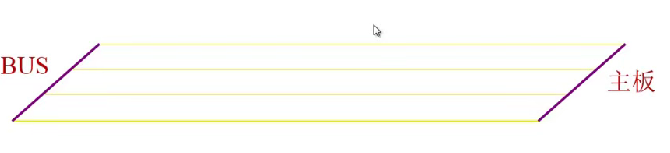

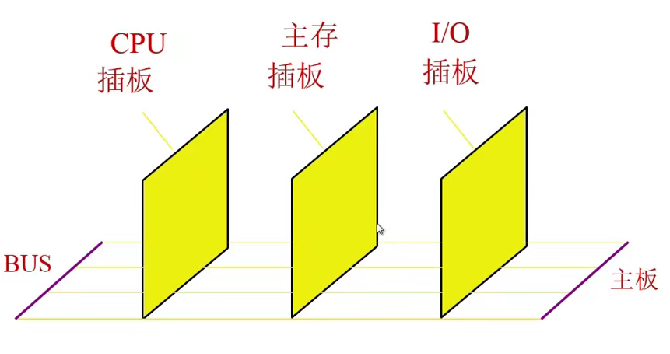

4.1 总线物理实现

- 实现方式:现代计算机总线通过印刷电路板实现,这块电路板称为主板或模板

- 连接部件:主板上留有接口用于连接CPU插板、存储插板和I/O设备插板

- 典型结构:采用主板+插板架构,各功能模块通过标准化接口接入总线系统

4.2 总线的特性

1)机械特性 – 尺寸、形状、管脚数 及 排列顺序

- 定义:保证插板与总线物理连接的参数

- 具体内容:

- 尺寸规格:插槽与插板的匹配尺寸

- 形状设计:连接器的物理外形

- 管脚数量:信号线的总数

- 排列次序:各信号线的位置顺序

2)电气特性 – 传输方向 和有效的电平 范围

- 信号方向:

- 数据线:双向传输(如D0-D15)

- 地址线:单向传输(如A0 – A31 从CPU发出)

- 电平规范:

- 高电平范围:如3.3V ± 0.3V表示 逻辑1

- 低电平范围:如0V ± 0.5V表示 逻辑 0

- 驱动能力:信号线的最大负载能力

3)功能特性

- 信号分类:

- 地址信号:指定访问位置(如内存地址)

- 数据信号:传输内容信息(如8/16/328/16/328/16/32位数据)

- 控制信号:协调操作时序(如读/写信号)

- 状态信号:反馈当前状态(如就绪/忙信号)

- 典型示例:8086处理器的20位地址总线中,16位复用为数据总线

4)时间特性 – 信号的时序关系

- 时序要求:各信号间的严格时间关系

- 关键参数:

- 建立时间(Setup Time)

- 保持时间(Hold Time)

- 时钟周期(Clock Cycle)

- 同步方式:包括同步时序和异步时序两种基本类型

4.3 总线的性能指标

1、总线宽度:数据线根数决定并行传输位数

2、标准传输率:每秒传输的最大字节数(MBps)(兆字节/秒)

3、时钟特性:

- 同步方式:有无统一时钟信号

- 时钟频率:如33MHz、66MHz等

4、总线复用:地址线与数据线复用(为了减少芯片的管脚数,芯片的封装体系减小)

5、信号线数:地址线、数据线和控制线的总和

6、总线的控制方式:突发、自动、仲裁、逻辑、计数

7、负载能力等性能指标

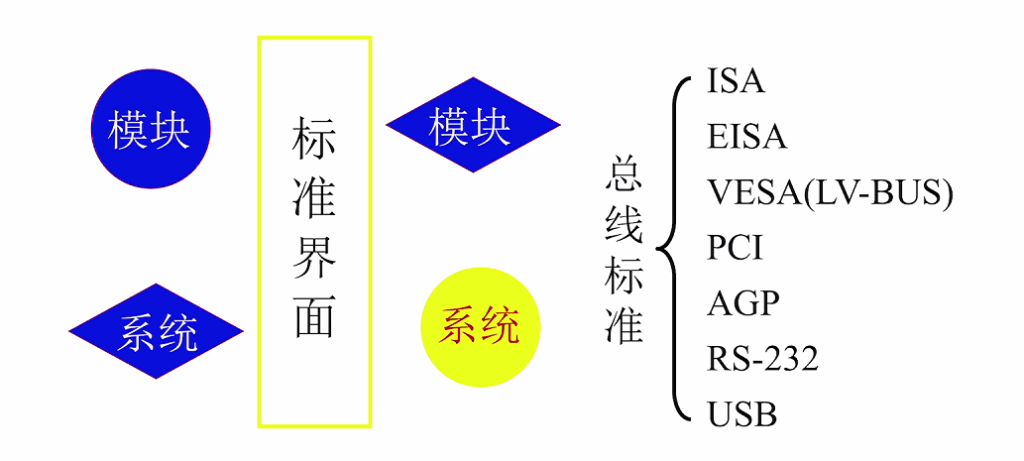

五、总线的标准

5.1 总线标准定义

标准化必要性:实现不同厂商设备的兼容互联

- 标准内容:包括机械、电气、功能、时间四方面规范

- 发展历程:从低速简单总线向高速可扩展总线演进

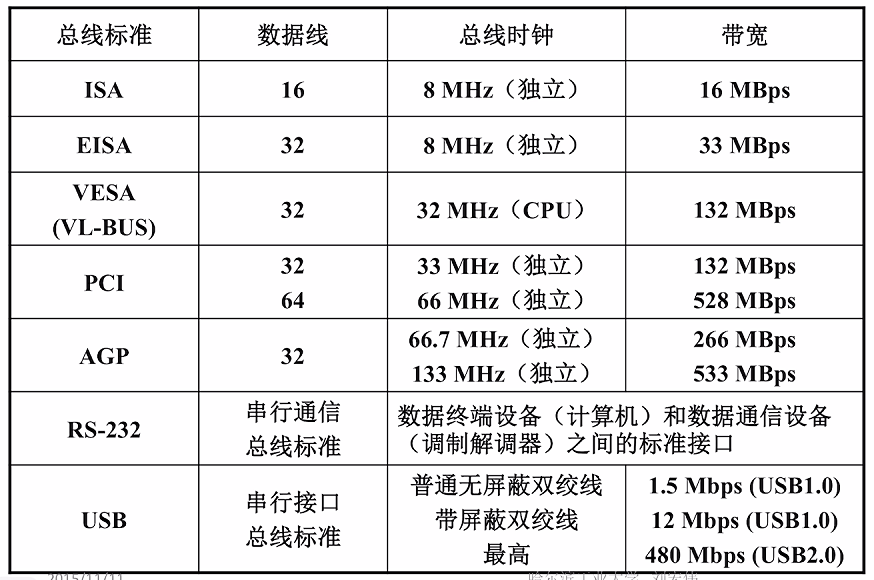

5.2 各总线标准定义

六、总线的结构

6.1 单总线结构

- 连接方式:将所有设备(CPU、主存、I/O设备)都连接到一条系统总线上

- 主要问题:总线成为系统性能瓶颈,所有数据传输都需要通过同一条总线

- 典型特征:结构简单但效率低,当多个设备同时请求总线时会产生竞争

6.2 多总线结构 – 双总线结构

- 组成要素:

- 主存总线:连接CPU和主存储器

- I/O总线:连接各种I/O设备

- 通道:连接两条总线的特殊处理器

- 通道特点:

- 结构简单的专用处理器

- 有独立控制器和指令系统

- 能执行通道程序(由操作系统编写)

- 典型应用:IBM体系结构中的I/O处理

- 优势:分离存储和I/O操作,减轻总线负载

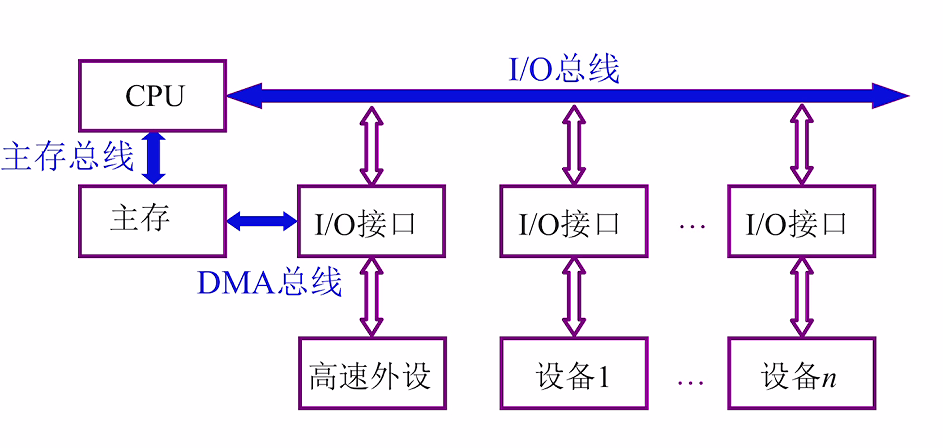

6.3 多总线结构 – 三总线结构

- 总线组成:

- I/O总线:连接低速设备

- 主存总线:连接CPU和主存

- DMA总线:专用于高速设备直接访问内存

- DMA特性:

- 全称:直接存储器访问(Direct Memory Access)

- 功能:允许外设直接与内存交换数据,不经过CPU

- 适用场景:高速外设(如磁盘、网络接口等)

- 工作方式:

- 高速设备通过DMA总线直接访问内存

- 低速设备仍通过I/O总线与CPU交互

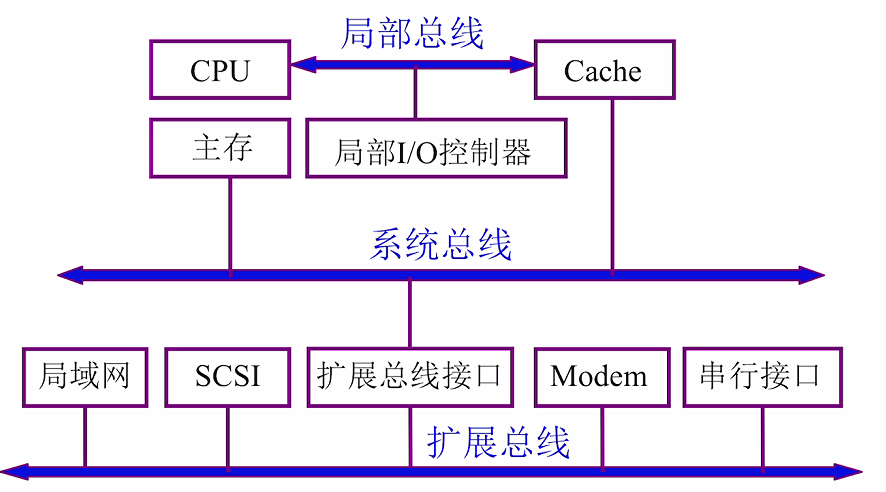

6.4 多总线结构 – 三总线结构其他形式

- 层次结构:

- 局部总线:连接CPU、Cache和局部I/O控制器

- 系统总线:通过扩展总线接口连接扩展总线

- 扩展总线:连接各类外设

- Cache作用:

- 解决CPU与内存速度不匹配问题(CPU年增长52% vs 内存十年才快一倍)

- 小容量高速缓存,存储CPU常用指令和数据

- 存在问题:不同速度设备混接在扩展总线,影响高速设备性能

CPU性能大概每年提高52%

内存每10年才能提升一半

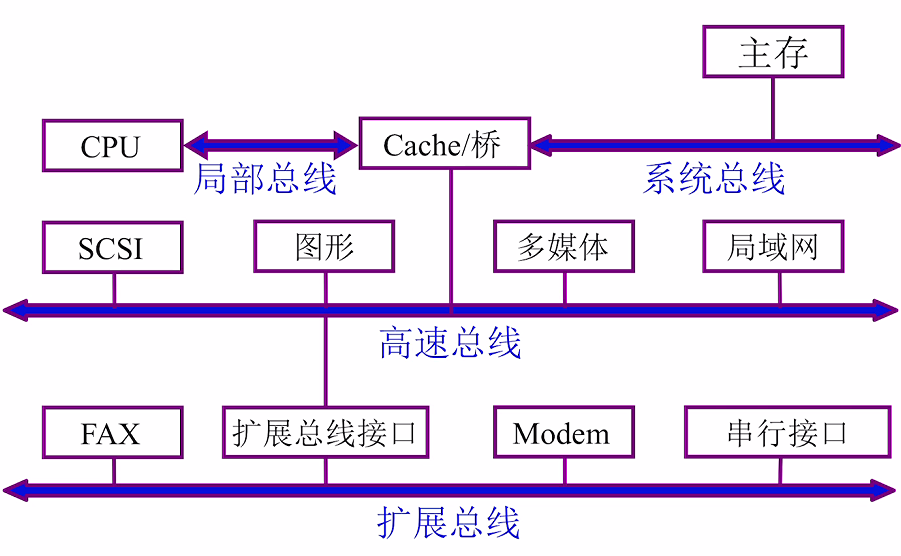

6.5 多总线结构 – 四总线结构

- 总线分类:

- 局部总线:CPU与Cache/桥的连接

- 系统总线:连接主存和桥

- 高速总线:连接图形、多媒体等高速设备

- 扩展总线:连接Modem等低速设备

- 设计特点:

- 通过桥电路实现总线扩展

- 严格区分高速/低速设备,分别使用不同总线

- 典型高速设备:SCSI、图形设备、局域网接口

- 典型低速设备:串行接口、传真Modem

七、总线结构的举例

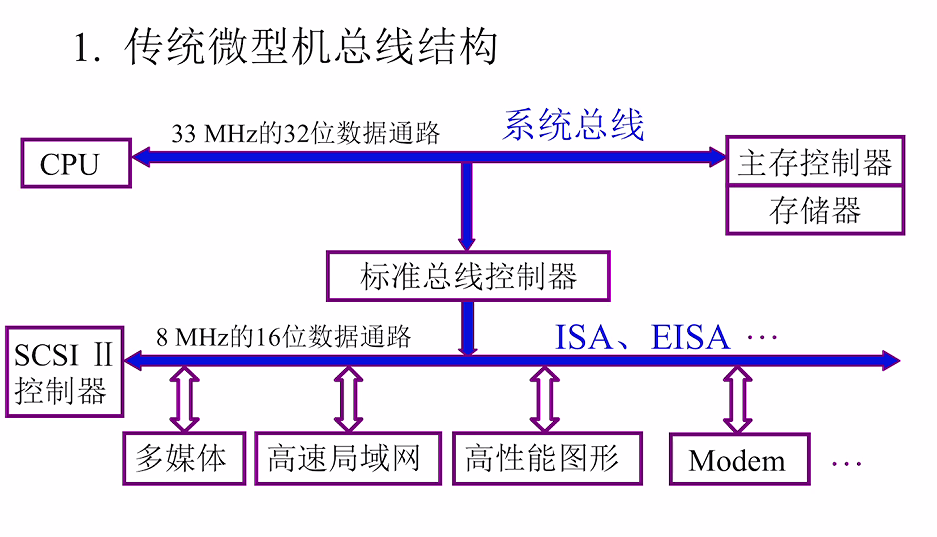

7.1 传统微型机总线结构

- 原理:通过标准总线控制器把系统总线和I/O总线进行分离

- 连接方式:

- 系统总线直连CPU和存储器

- 通过标准总线控制器扩展I/O总线

- 支持SCSI、ISA、EISA等多种接口标准

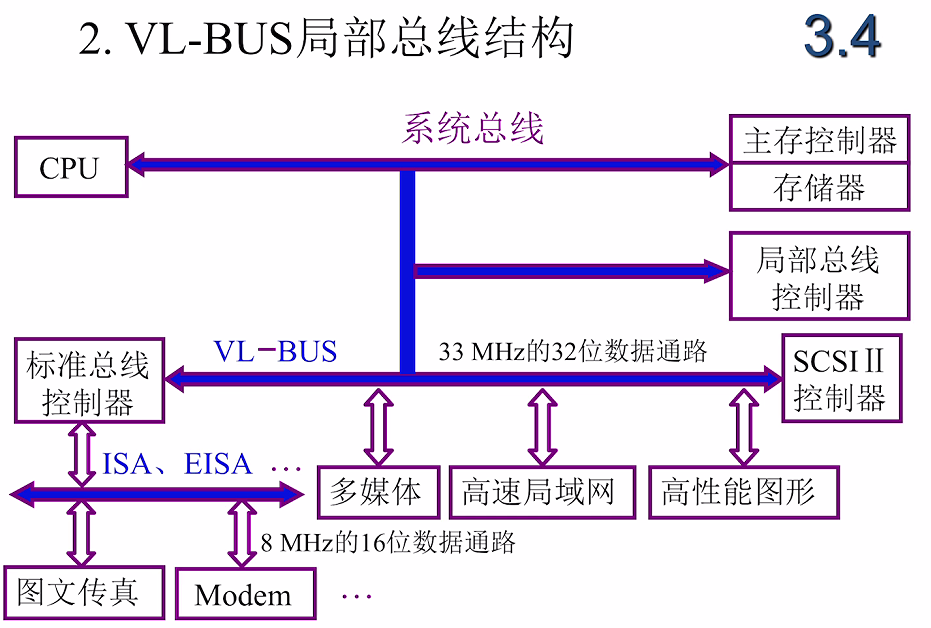

7.2 VL-BUS局部总线结构

- 改进要点:

- 新增VL-BUS高速局部总线(33MHz/32位)- 连接高速设备

- 保留标准总线(8MHz/16位)连接低速设备

- 设备分配:

- 高速总线:连接图形设备等高性能外设

- 低速总线:连接传统ISA/EISA设备

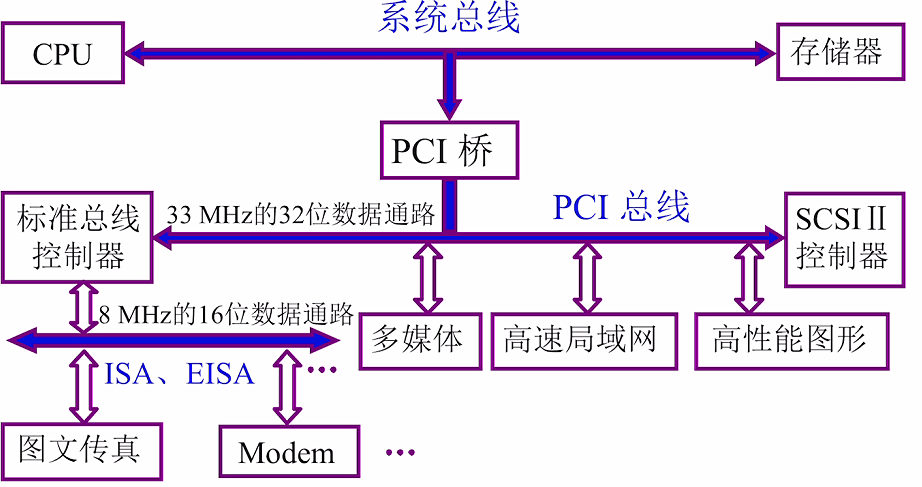

7.3 PCI总线结构

- 核心组件:

- PCI桥:连接系统总线与PCI总线

- PCI总线:33MHz的32位高速通路

- 优势:

- 更好的设备兼容性

- 支持热插拔

- 广泛用于多媒体、高速网络等场景

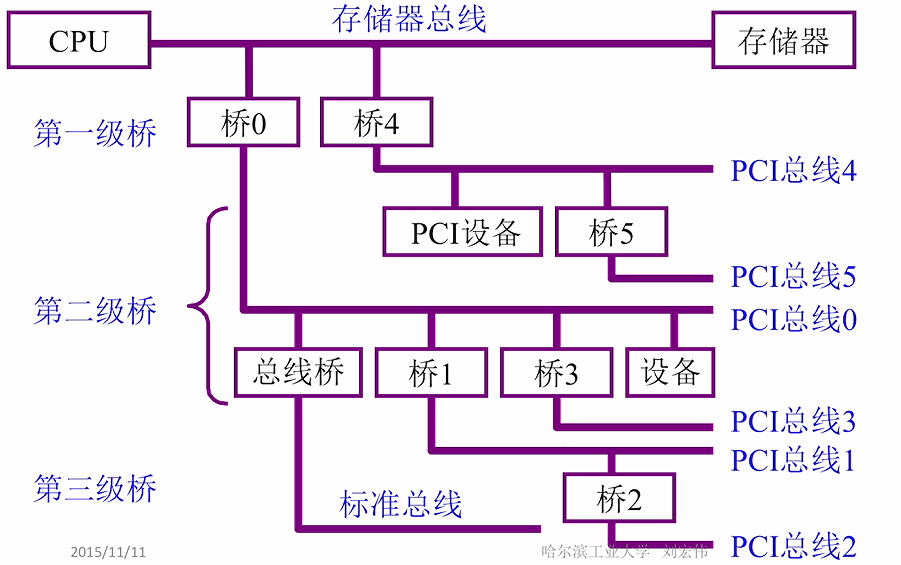

7.4 多层PCI总线结构

- 扩展原理:

- 通过多级桥电路实现总线层级扩展

- 每级桥可连接新的PCI总线和设备

- 典型结构:

- 存储器总线:CPU与主存专用

- 一级桥:连接主PCI总线

- 二级桥:扩展更多PCI总线

- 三级桥:最终连接标准总线

- 应用价值:解决单一总线驱动能力不足的问题,支持更多设备接入

本网站原创文章版权归何大锤的狂飙日记所有。发布者:何大锤,转转请注明出处:何大锤的博客