一、冯诺依曼计算机

1、冯·诺依曼计算机的特点

1.1 核心特征: 存储程序结构,程序和数据以二进制形式存放在计算机中

1.2 历史背景: 由美籍匈牙利科学家冯·诺依曼提出,1949年第一台冯·诺依曼结构机器EDVAC研制成功

1.3 冯诺依曼六大特点:

1、五大部件组成: 运算器、控制器、存储器、输入设备和输出设备

2、混合存储: 指令和数据以同等地位存放在存储器中,按地址寻访

3、二进制表示: 指令和数据都用二进制数010101表示

4、指令结构: 由操作码和地址码组成,操作码指明操作类型,地址码指明操作数位置

5、存储程序: 程序存放在存储器中

6、运算中心: 以运算器为中心,都称为冯诺依曼计算机(核心)

思考延伸

部件合并: 如算盘将运算器、存储器和输出设备统一为算盘珠

存储分离: 现代计算机将指令和数据分别存放在指令Cache和数据Cache中

进制选择: 二进制表示的理论依据和未来可能的多进制表示

操作码扩展: 如IBM 360中加法运算根据基值、长度不同分为8种

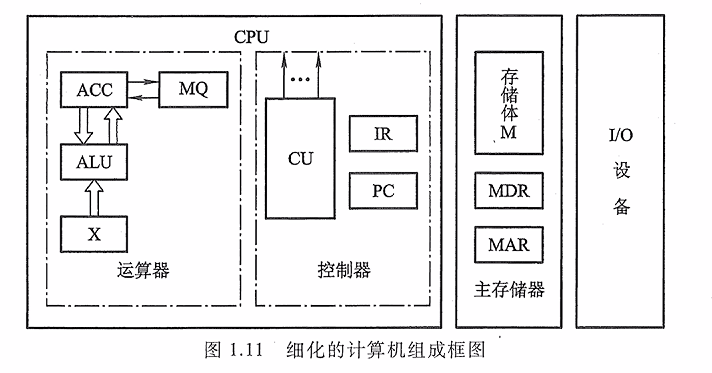

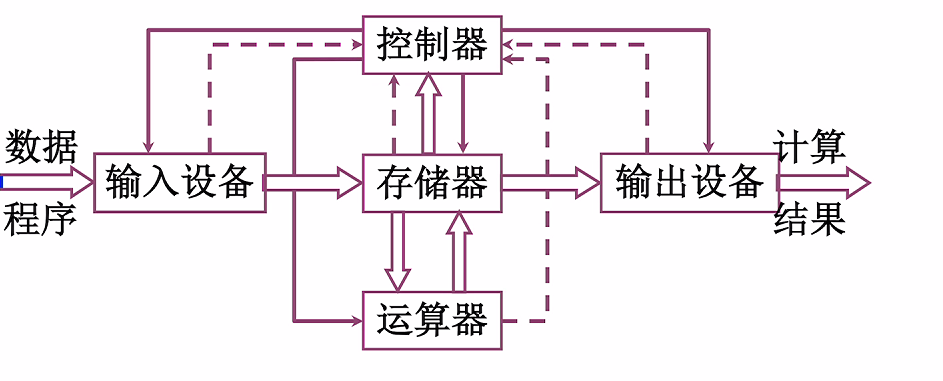

2、冯·诺依曼计算机硬件框图

1、硬件组成

- 运算器: 核心部件,完成算术和逻辑运算

- 存储器: 存放程序和数据

- 控制器: 指挥程序运行,控制指令执行顺序

- 输入设备: 将人类信息转换为机器可识别形式

- 输出设备: 将处理结果转换为人类可识别形式

2、数据流向

- 数据通路: 黑色实线表示数据流动路径

- 控制反馈: 虚线表示控制和状态反馈

- 中心结构: 所有输入输出必须经过运算器

3、现存问题

- 运算器瓶颈: 同时承担运算和I/O任务,导致系统性能受限

- 改进方向: 考虑改变以运算器为中心的结构设计

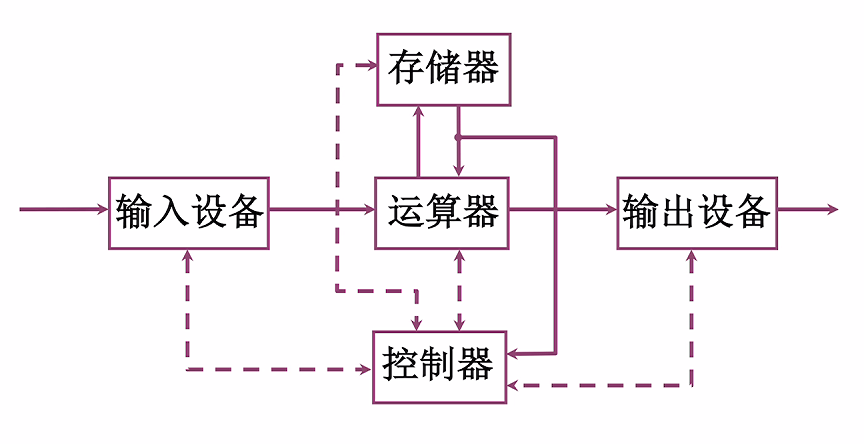

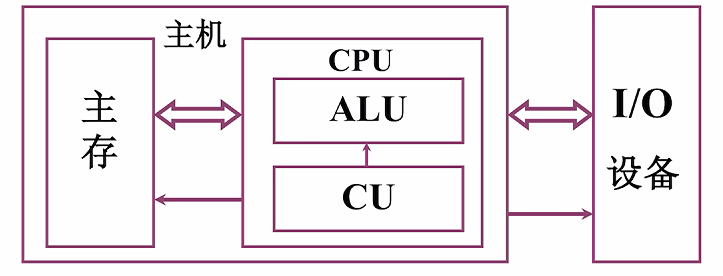

3、以存储器为中心的计算机硬件框图

1、结构改进原因:

冯诺依曼结构存在两个主要问题:一是以运算器为中心导致运算器成为系统瓶颈;二是结构混乱缺乏层次化特征

2、核心改进点:将运算器为中心改为存储器为中心,实现输入输出设备与存储器直接交换信息

3、数据传输机制:双线表示数据传输路径,数据可通过输入设备直接存入存储器,运算器从存储器获取数据并将结果存回存储器,输出时数据直接从存储器送到输出设备

3、控制机制:控制器通过控制信号和状态反馈信号对整个系统进行控制和状态感知

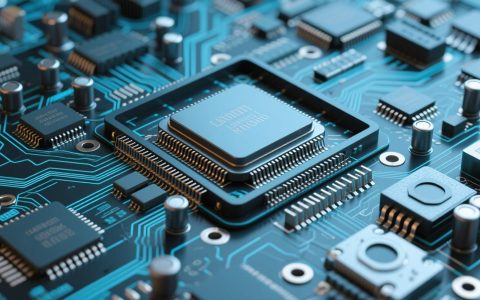

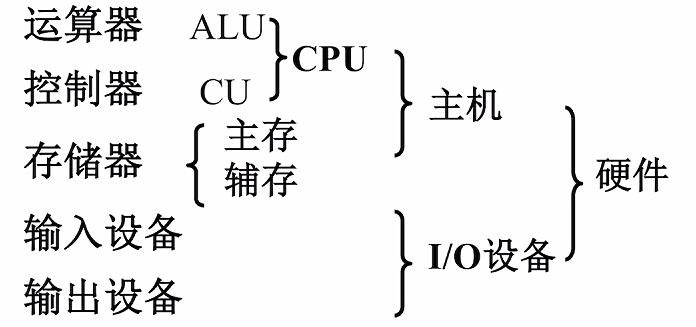

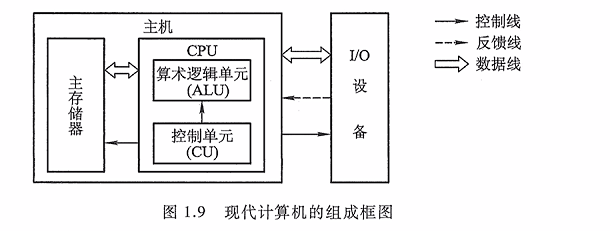

二、现代计算机

2.1 模块划分

- CPU包含运算器(ALU)和控制器(CU)

- 存储器分为主存和辅存

- 主机系统包含CPU和主存

- I/O设备包含输入设备、输出设备和辅存

层次化结构:整个系统采用”大框套小框”的层次化表示方法,从整体到局部逐步细化

设计方法:通过将大模块分解为小模块,直到可用简单逻辑电路实现,再逆向组装成完整系统

2.2 系统复杂性管理的方法(3‘Y)

层次化Hierachy (Y1):将系统划分为多个模块/子模块,递归细化使大问题分解为易解决的小问题

模块化Modularity (Y2):每个模块需明确定义功能和接口,确保子模块能正确组装成更大模块

规则化regularity (Y3):使模块具有可重用性,接口和功能遵循工业/国际标准(如内存模块的标准化接口)

这种方法细化了计算机产业分工,企业可专注于特定部件的生产和优化

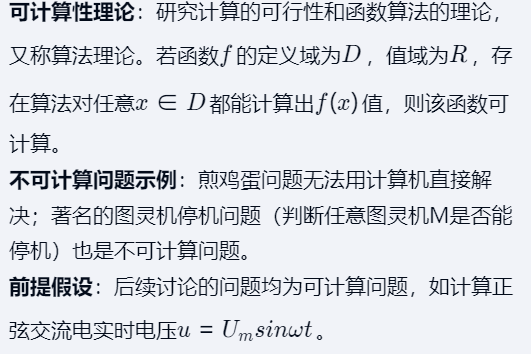

三、计算机问题细化(现实问题用计算机解决)

一个现实种的问题,如何用计算机来解决?

是不是所有的问题都可以用计算的方法来解决?

假设我们面对的是一个可以有计算机解决的问题,如何用计算机来解决这个问题呢?

3.1 上机前的准备

- 1、建立数学模型

- 2、确立计算方法

包含建立数学模型→确定计算方法→编写程序三个步骤

- 3、编写解题程序

- 程序 – 运算的全部步骤

- 指令 – 每一个步骤

程序本质:由指令构成的运算步骤集合,每条指令对应一个操作步骤,指令本身又包含微步骤(可用微指令表示)。

程序执行:需要在计算机系统上有序执行。

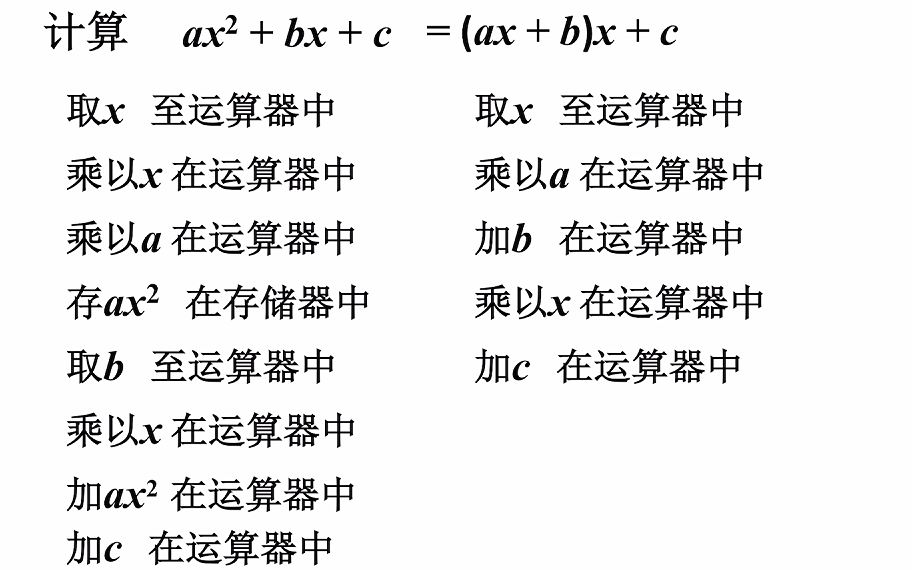

3.2 编程举例

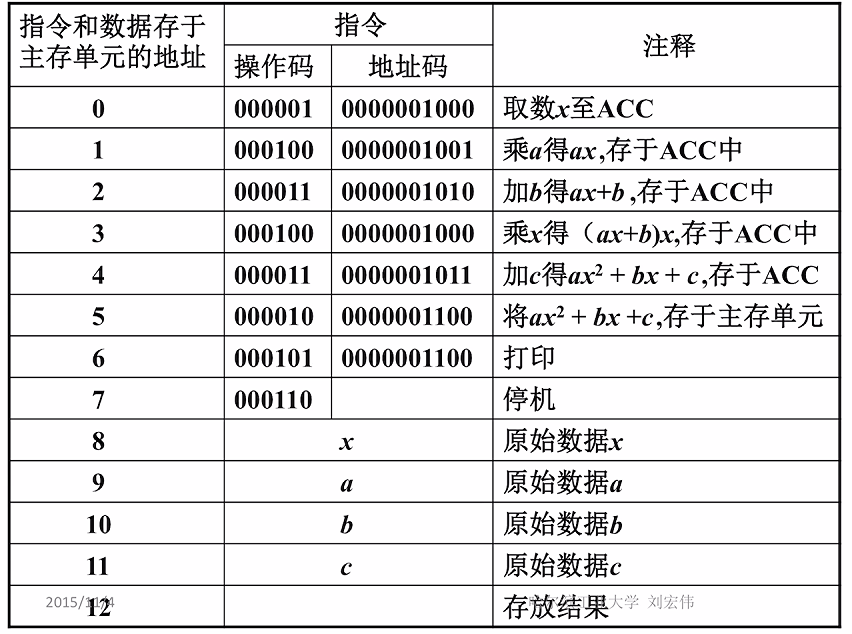

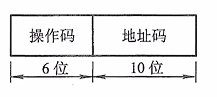

指令结构:16位二进制,前6位为操作码,后10位为地址码。

典型指令:

取数指令:操作码000001,功能[α]→ACC[α]→ACC[α]→ACC

存数指令:操作码000010,功能ACC→[β]ACC→[β]ACC→[β]

加法指令:操作码000011,功能ACC+[γ]→ACCACC+[γ]→ACCACC+[γ]→ACC

乘法指令:操作码000100,需注意结果可能超出寄存器位数

程序清单

冯诺依曼结构特征:指令和数据以同等地位存储在存储器中,均用二进制表示。

存储分布:内存单元0-7存储指令(含操作码和地址码),8-11存储原始数据x/a/b/c,12单元存储计算结果。

指令执行流程:通过存储程序方式将指令和数据存入内存后,系统按序执行指令。

四、存储器

4.1 存储器的基本组成

4.1.1 存储体

存储体(大楼)- 存储单元(房间)- 存储元件(0 / 1)(床位有无人)

存储体核心结构:由多个存储单元构成,用于保存指令和数据(01代码)

存储单元类比:相当于大楼中的房间,每个房间有唯一编号(地址)

存储元件:存储单元由多个存储元件构成,类似房间中的床位,用0/1表示占用状态

存储字:存储单元中存放的二进制代码组合称为存储字

存储字长:存储单元中二进制代码的位数,决定数据存储容量

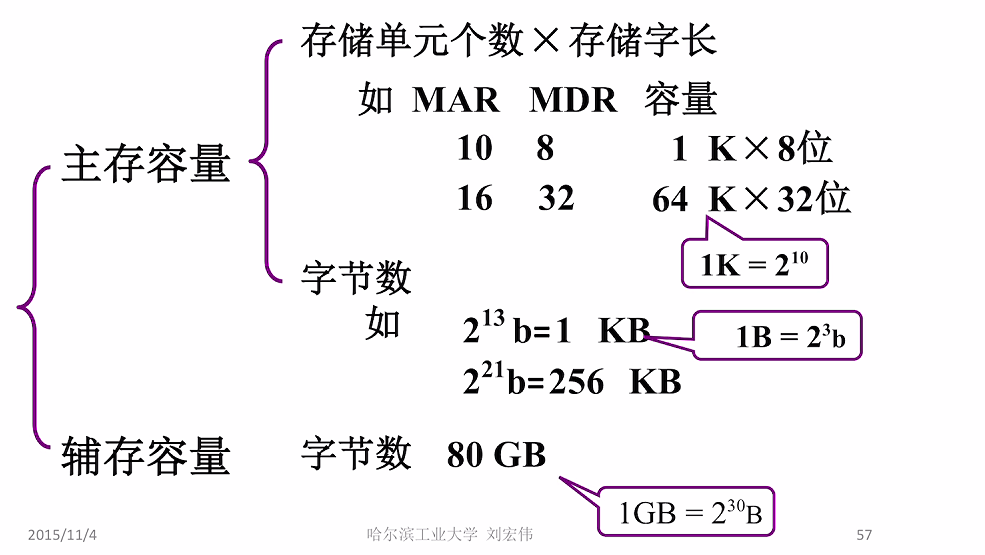

4.1.2 MAR – Memory Address Register(存储器地址寄存器)

反映存储单元的个数

功能:保存存储单元的地址或编号

命名来源:M(Memory)+A(Address)+R(Register)

位数决定:与存储单元数量直接相关(如4位MAR可寻址24=162^4=1624=16个单元)

4.1.3 MDR – Memory Data Register(存储器数据寄存器)

功能:暂存CPU与存储体间传输的数据(读取/写入)

长度特性:与存储字长相同(如8位MDR对应8位存储字)

4.1.3 MAR 与 MDR的工作过程:

读取:CPU通过MAR给出地址→从对应存储单元取出数据→存入MDR

写入:CPU将数据存入MDR→通过MAR指定地址→写入存储单元

示例说明:

- 当MAR=4位,MDR=8位时:

- 可寻址范围:24=16个存储单元

- 每个单元容量:8位二进制数据

说明存储单元个数16,存储字长8

五、运算器

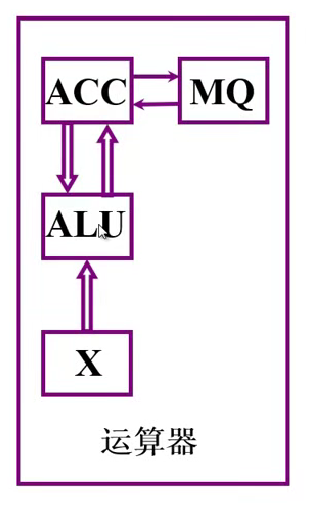

运算器是如何工作的? 比如:加减、乘除、或与非逻辑操作

运算器的功能是说明?如何工作的?

5.1 运算器的功能

基本功能:运算器最基本的功能是完成算术和逻辑运算,其核心是算术逻辑单元(ALU)。

电路特性:ALU通常是一个组合电路,特点是输入撤销时输出结果也会相应撤销。

数据保存:为了使ALU能够保存运算结果,必须在输入端加上寄存器。

5.2 运算器的基本组成及操作过程

ALU(Arithmetic Logic Unit):算术逻辑单元

3个寄存器

ACC(Accumulator):累加器,保存被加数/被减数/被乘数/被除数,同时保存运算结果

X:操作数寄存器,保存加数/减数/被乘数/除数

MQ(Multiplier-Quotient Register):乘商寄存器,乘法时保存乘数和结果低位,除法时保存商

- 不同的机器运算器结构不同

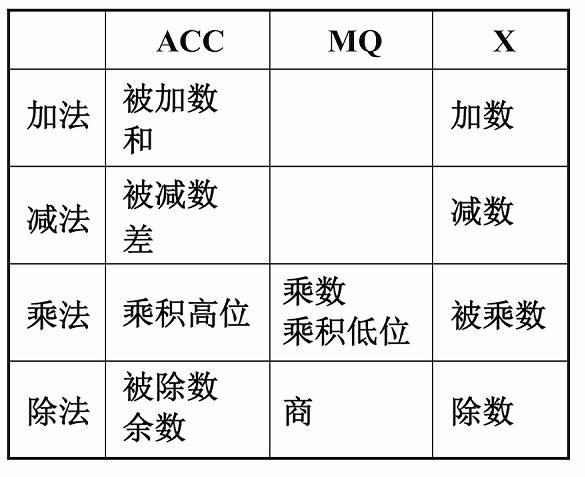

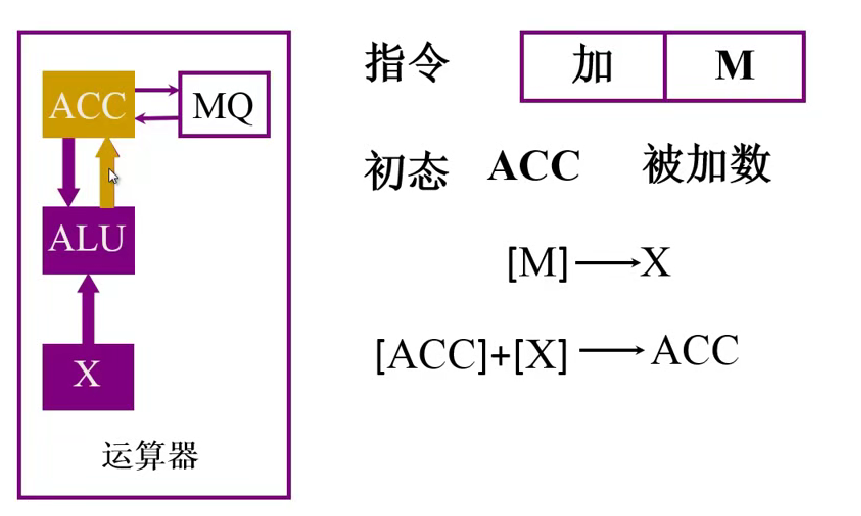

5.3 加、减、乘、除法操作的过程

5.3.1 加法操作

- 操作数分配:

- 被加数:保存在ACC中

- 加数:保存在X寄存器中

- 结果:和保存在ACC中

- 指令特点:单地址指令,隐含一个操作数在ACC中

- 执行过程:

- 取数指令将被加数存入ACC

- 加法指令将内存单元M的内容(加数)送入X

- ALU执行加法并将结果存入ACC

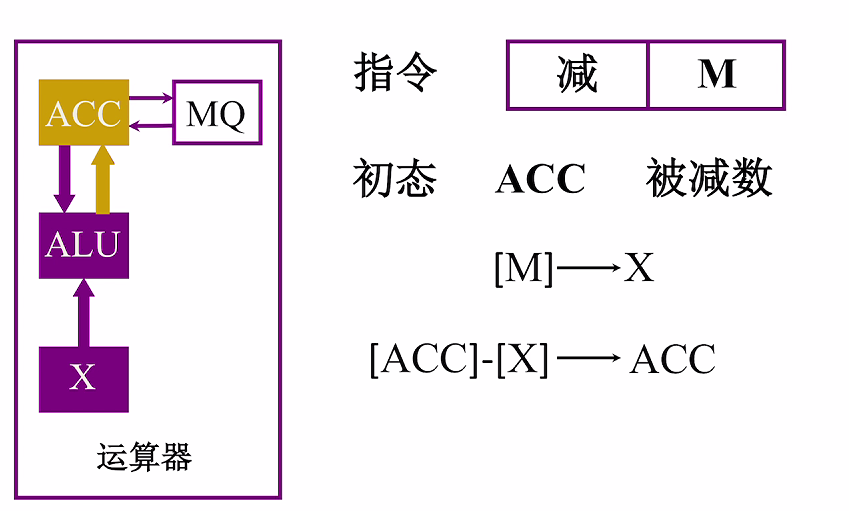

5.3.2 减法操作

- 操作数分配:

- 被减数:保存在ACC中

- 减数:保存在X寄存器中

- 结果:差保存在ACC中

- 指令格式:与加法类似,也是单地址指令

- 执行过程:

- 取数指令将被减数存入ACC

- 减法指令将内存单元M的内容(减数)送入X

- ALU执行减法并将结果存入ACC

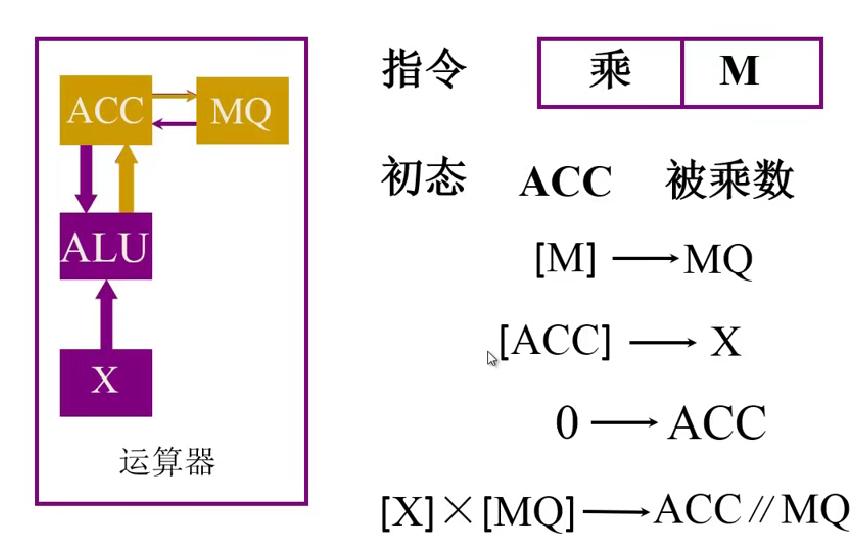

5.3.3 乘法操作

- 操作特点:通过加法和移位实现,类似笔算乘法

- 操作数分配:

- 被乘数:初始在ACC,后转移到X

- 乘数:保存在MQ中

- 结果:高位在ACC,低位在MQ

- 执行过程:

- 取数指令将被乘数存入ACC

- 乘法指令将内存单元M的内容(乘数)送入MQ

- 将ACC内容(被乘数)送入X

- 清零ACC

- ALU执行乘法(累加和移位)

- 结果高位存入ACC,低位存入MQ

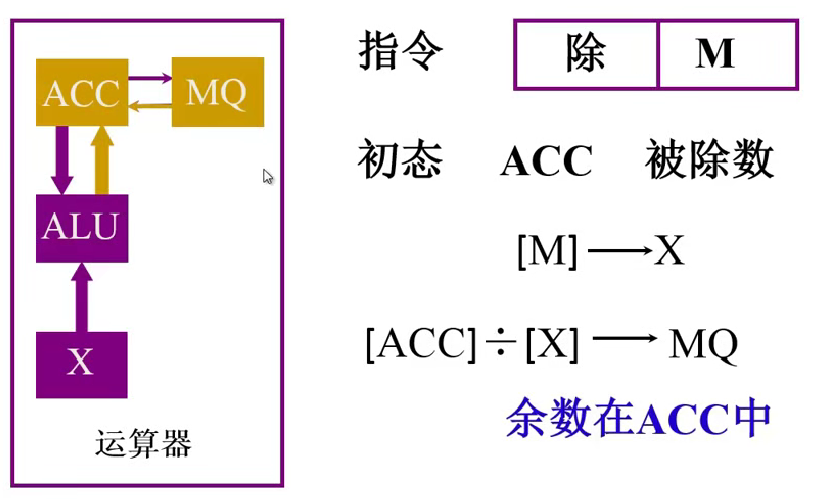

5.3.4 除法操作

- 操作特点:通过减法和移位实现

- 操作数分配:

- 被除数:保存在ACC中

- 除数:保存在X寄存器中

- 结果:商在MQ中,余数在ACC中

- 执行过程:

- 取数指令将被除数存入ACC

- 除法指令将内存单元M的内容(除数)送入X

- ALU执行除法(减法和移位)

- 商存入MQ,余数存入ACC

六、控制器

控制器的基本结构如何?

控制器的功能?解释指令

6.1 控制器的基本组成

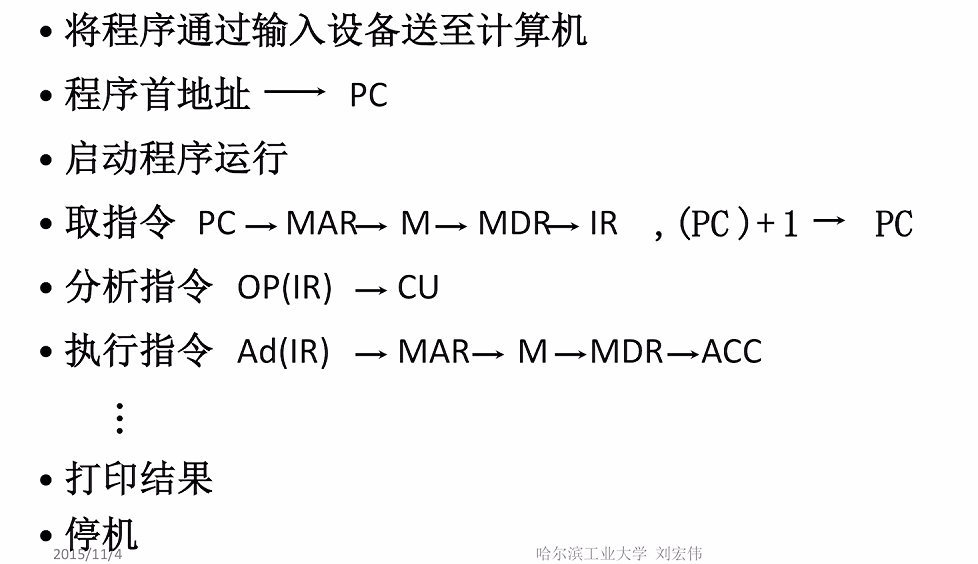

完成一条指令操作的取指、分析和执行 3 个阶段

- 取指令:程序计数器(Pro Counter)PC – 存放当前预执行指令的地址,具有计数功能(PC)+ 1 -> PC (执行完当前指令后PC值自动调整(通常+1,具体增量与机器结构相关))

- 分析指令:指令寄存器(Instruction Register) IR – 存放当前欲执行的指令

- 执行指令:控制单元 CU

- 工作流程:

- 取指令:PC→MAR→存储体→MDR→IR

- 分析指令:IR操作码→CU译码

- 执行指令:CU发出控制信号驱动执行部件

七、总结

- 主机三要素:运算器、控制器、存储器共同构成计算机主机

- 完整系统:主机加上I/O设备组成完整的计算机硬件系统

- 寄存器网络:

- 运算器含ALU、ACC、X、MQ寄存器

- 控制器含CU、IR、PC寄存器

- 存储器含存储体、MAR、MDR寄存器

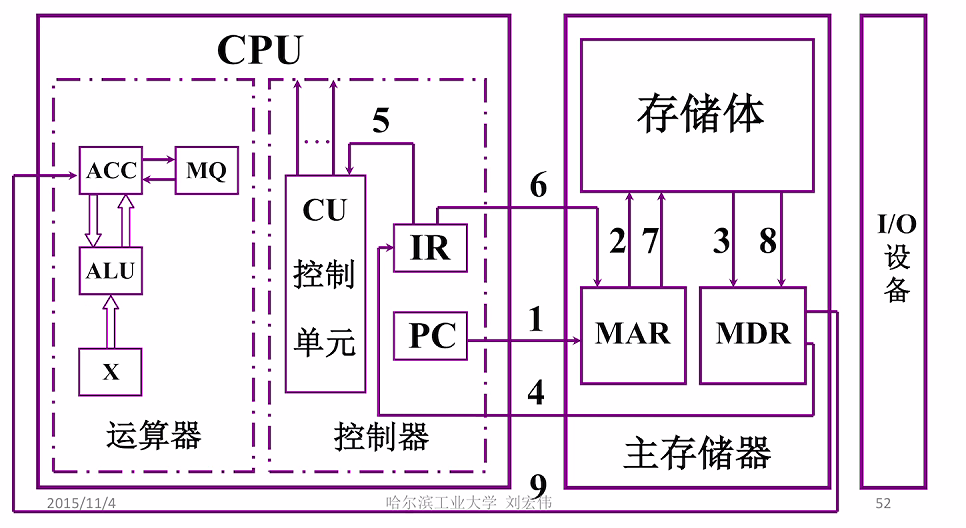

八、主机完成一条指令的过程

思考:

一条指令在主机上的完成过程?

程序在主机上是如何执行的?

8.1 以取数指令为例(保存在内存单元【M】中的数据,取到ACC寄存器中)

- 取指阶段:1、2、3、4

- PC→MAR→存储体(送指令地址)

- 存储体→MDR→IR(取指令)

- 分析阶段:5

- IR操作码→CU译码(识别为取数指令)

- 执行阶段:6、7、8、9

- IR地址码→MAR→存储体(送操作数地址)

- 存储体→MDR→ACC(取数操作)

- PC更新:在取指阶段结束后立即执行PC+1→PC

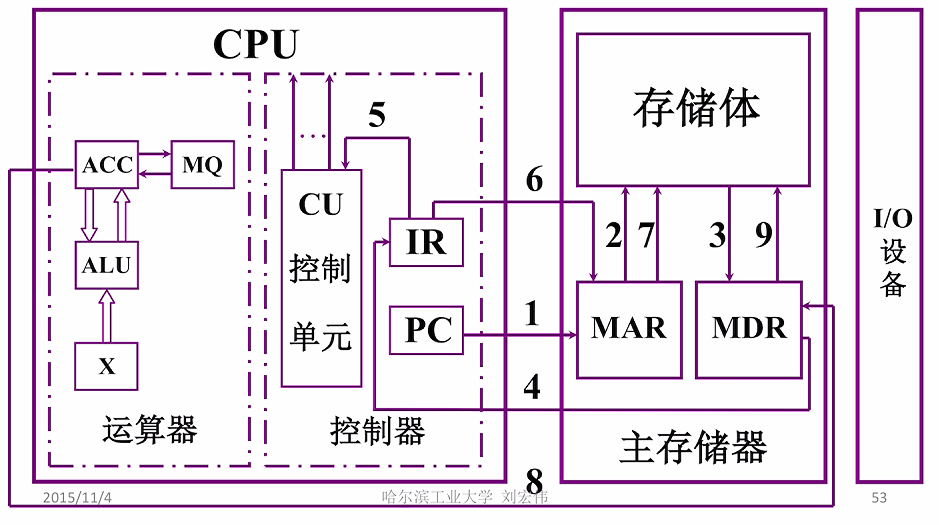

8.2 以存数指令为例(把ACC中保存的数据放到存储体中指定存储单元中)

- 取指阶段:(指令的地址初态存放在PC中)1、2、3、4

- PC→MAR→存储体(同取数指令)

- 存储体→MDR→IR

- 分析阶段:5

- IR操作码→CU译码(识别为存数指令)

- 执行阶段:6、7、8、9

- IR地址码→MAR(送存储地址)(MAR告诉存储体有一个数据要进来,地址是多少)

- ACC→MDR→存储体(存数操作)

- 通用流程:所有指令的取指阶段操作完全相同,区别仅在于分析执行阶段

除此之外还有加法、乘法、打印指令

8.3 ax2+bx+c程序的运行过程

几个说明的点:

1、OP(IR):IR – 指令寄存器保存了指令、OP – 操作码

2、PC在取指令的操作结束后完成+1

3、操作码和地址码

操作码表示机器所执行的各种操作,如取数、存数、加、减、乘、除、停机、打印等。

地址码表示参加运算的数在存储器内的位置。

九、计算机硬件主要技术指标

9.1 机器字长

CPU一次能处理数据的位数与CPU中的寄存器位数有关

- 基本定义: 例如处理两个8位二进制数相加的CPU,其字长为8位。

- 性能影响: 字长越长性能越好。64位运算在8位机上需8次加法,而在64位机上只需1次。

- 存储关联: 在模型机中,存储字长与寄存器长度相同,但实际计算机可能不同

9.2 运算速度

1、主频

2、核数与线程数

3、吉普森法

- 频率类型:

- 静态频率:通过程序清单统计,不用执行

- 动态频率:通过实际执行统计,计算程序过程中,每一条指令出现的频率,结果更精确

4、CPI – 执行一条指令所需时钟周期数

- 时钟周期指标: 表示执行一条指令所需时钟周期数,理想状态是1个周期完成1条指令。

- 计算方法: 需对指令集中所有指令的CPI求加权平均

5、IPC – 与CPI相反,表示单个时钟周期能完成的指令数,超标量计算机常用此指标。

6、MIPS

指令指标: 表示每秒执行百万条指令数,但需注意指令复杂度的影响。

局限性: 不能单纯比较MIPS值,需考虑单条指令完成的运算量。

7、FLOPS 每秒浮点运算次数

9.3 存储容量

- 存放二进制信息的总位数

分为主存容量、辅存容量

本网站原创文章版权归何大锤的狂飙日记所有。发布者:何大锤,转转请注明出处:何大锤的博客